### МИНИСТЕРСТВО ОБРАЗОВАНИЯ И НАУКИ РОССИЙСКОЙ ФЕДЕРАЦИИ

Федеральное государственное автономное образовательное учреждение высшего образования

## «Дальневосточный федеральный университет» (ДВФУ)

#### ШКОЛА ЕСТЕСТВЕННЫХ НАУК

«СОГЛАСОВАНО»

Руководитель ОП

«УТВЕРЖДАЮ»

Заведующий кафедрой

компьютерных систем

Отмине Должиков С.В.

STON WIX HAVE

«\_18\_» \_июня\_\_\_\_ 2015\_ г.

\_18\_»\_июня\_8 \_\_\_\_2015\_ г

Кулешов Е.Л.

### РАБОЧАЯ ПРОГРАММА УЧЕБНОЙ ДИСЦИПЛИНЫ

Цифровая электроника

#### Направление подготовки 09.03.02 Информационные системы и технологии

профиль «Информационные системы и технологии в связи» Форма подготовки очная

курс 4 семестр 7

лекции 36 час.

практические занятия - 0 час.

лабораторные работы 72 час.

в том числе с использованием МАО 54 час. в интерактивной форме

в том числе в электронной форме лек. - час. /пр. - /лаб. - час.

всего часов аудиторной нагрузки 108 час.

в том числе с использованием МАО 54 час.

самостоятельная работа 72 час.

в том числе на подготовку к экзамену 27 час.

курсовая работа / курсовой проект - не предусмотрены

зачет 7 семестр

экзамен 7 семестр

Рабочая программа составлена в соответствии с требованиями федерального государственного образовательного стандарта высшего образования, утвержденного приказом Министерства образования и науки от 12.03.2015 г. № 219.

Рабочая программа обсуждена на заседании кафедры компьютерных систем, протокол № 14 от «18» июня 2015 г.

Заведующий (ая) кафедрой Кулешов Е.Л.

Составитель (ли): д.ф.-м..н., профессор Цуканов Д.А.

| г. гаоочая программа | пересмотрена на  | заседан  | ни кафедры.    |

|----------------------|------------------|----------|----------------|

| Протокол от «» _     |                  | _201     | r. №           |

| Ваведующий кафедрой  | i                |          |                |

| Заведующий кафедрой  | (подпись)        |          | (И.О. Фамилия) |

|                      |                  |          |                |

|                      |                  |          |                |

|                      |                  |          |                |

|                      |                  |          |                |

|                      |                  |          |                |

|                      |                  |          |                |

|                      |                  |          |                |

|                      |                  |          | _              |

| I. Рабочая программ  | а пересмотрена н | а заседа | нии кафедры:   |

| Тротокол от «»       |                  |          |                |

| Заведующий кафедрой  | ii               |          | _              |

|                      | (подпись)        |          | (И.О. Фамилия) |

#### Аннотация

Учебная дисциплина «Цифровая электроника» разработана для студентов 4 курса направления подготовки бакалавриата 09.03.02 Информационные системы и технологии, профиль «Информационные системы и технологии в связи», в соответствии с требованиями федерального государственного образовательного стандарта высшего образования, утвержденного приказом Министерства образования и науки РФ от 12.03.2015 № 219.

Дисциплина «Цифровая электроника» входит в базовую часть блока «Дисциплины (модули)» образовательной программы, реализуется на 4 курсе, в 7 семестре. Общая трудоемкость освоения дисциплины составляет 6 ЗЕ (216 час.). Учебным планом предусмотрены лекции (36 час.), лабораторные работы (72 час.), самостоятельная работа студента (108 час.).

Курс посвящён принципам работы цифровых электронных устройств, их структуре и особенностям их применения. Рассматриваются основные типы цифровой аппаратуры, алгоритмы их работы. Изучаются наиболее типичные схемотехнические решения и тенденции их развития. Особое внимание уделено наиболее перспективным микропроцессорным системам.

В курсе рассматриваются ключевые принципы цифровой электроники, особенности цифровых сигналов, способы организации взаимодействия элементов, узлов и устройств цифровых систем. Исследуются алгоритмы функционирования базовых элементов и основные схемы их включения, а также их объединения в составе устройств и систем. Приведены базовые сведения о двоичной логике, о цифровых сигналах, кодах, синхронизации, обозначениях на схемах. Рассмотрены логические элементы с жёсткой логикой работы и с программируемым алгоритмом работы. Описаны принципы построения и применения оперативных и постоянных запоминающих устройств. Приведены принципы организации микропроцессорных систем и взаимодействия их составных частей. Исследованы различные методы обмена информацией и их практическая реализация.

Цель изучения дисциплины - освоение методологических основ цифровой электроники, овладение основами теории построения логических схем, знакомство с принципами формирования и основные характеристики двоичного сигнала, принципами работы и электрофизическими характеристиками основных цифровых устройств; методологией и технологиями проектирования и расчета цифровых узлов и компонентов.

Задачи изучения дисциплины:

- изучение основных стандартов проектирования цифровых устройств;

- приобретение умений и навыков по методологическим основам цифровой электроники;

приобретение умений и навыков в применении методик системного и детального проектирования цифровых узлов и компонентов, овладение соответствующим проектным

Дисциплина «Цифровая электроника» логически и содержательно связана с такими курсами, как «Основы микропроцессорной техники», «Основы электроники и электротехники», «Инструментальные средства информационных систем», «Языки ассемблера» и др.

В результате изучения данной дисциплины у обучающихся формируются следующие общепрофессиональные и профессиональные компетенции (элементы компетенций).

| Код и формулировка                                                  | Э                              | тапы формирования компетенции                                                                       |

|---------------------------------------------------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------|

| компетенции                                                         |                                |                                                                                                     |

| ОПК-3, способностью применять основные приемы и законы создания и   | знает (порого-<br>вый уровень) | разновидности чертежей и документации по аппаратным и программным компонентам информационных систем |

| чтения чертежей и документации по аппаратным                        | умеет (продви-<br>нутый)       | создавать и читать чертежи и документацию                                                           |

| и программным компо-<br>нентам информационных<br>систем             | владеет (высо-кий)             | автоматизированными комплексами для со-<br>здания чертежей и документации                           |

| ПК-13, способностью разрабатывать средства автоматизированного про- | знает (пороговый уровень)      | средства автоматизированного проектирования информационных технологий                               |

| 10Math3hpobamio10 hpo                                               | умеет (продви-                 | разрабатывать средства автоматизированного                                                          |

| ектирования информаци-                                | нутый)                         | проектирования информационных технологий                                                                                          |

|-------------------------------------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| онных технологий                                      | владеет (высо-кий)             | способностью разрабатывать средства автоматизированного проектирования информационных технологий                                  |

| ПК-20,<br>способностью проводить                      | знает (пороговый уровень)      | методы производственных и непроизводственных затрат                                                                               |

| оценку производственных и непроизводственных          | умеет (продви-<br>нутый)       | проводить оценку производственных и непро- изводственных затрат                                                                   |

| затрат на обеспечение качества объекта проектирования | владеет (высо-<br>кий)         | способностью проводить оценку производ-<br>ственных и непроизводственных затрат на<br>обеспечение качества объекта проектирования |

| ПК-29,<br>способностью проводить                      | знает (порого-<br>вый уровень) | принципы сборки информационной системы из готовых компонентов                                                                     |

| сборку информационной системы из готовых ком-         | умеет (продви-<br>нутый)       | проводить сборку информационной системы из готовых компонентов                                                                    |

| понентов                                              | владеет (высо-<br>кий)         | способностью проводить сборку информационной системы из готовых компонентов                                                       |

Содержание дисциплины охватывает круг вопросов, связанных с методологическими основами цифровой электроники. Изучая дисциплину, студенты осваивают: основы теории построения логических схем, принципы формирования и основные характеристики двоичного сигнала, принципы работы и электрофизические характеристики основных цифровых устройств; методологии и технологии проектирования и расчета цифровых узлов и компонентов.

# I. СТРУКТУРА И СОДЕРЖАНИЕ ТЕОРЕТИЧЕСКОЙ ЧАСТИ КУРСА лекции - 36 часов

### Тема 1. Введение в курс цифровой электроники (2 часа)

Лекция 1. Цифровая электронная схема. Цифровой сигнал. Применение цифровых схем. Приборы цифровой электроники (2 часа).

### Тема 2. Основы теории логических схем (10 час.)

Лекция 2. Логическая переменная. Логические высказывания. Системы исчисления: двоичная, десятичная, шестандцатеричная. (2 часа)

Лекция 3. Булева алгебра. Основные теоремы Булевой алгебры (теоремы с одной переменной, теоремы с двумя и более переменными). Таблица истинности. (2 часа)

Лекция 4. Булевы функции. Способы задания Булевых функций (словесный, табличный, алгебраичный, числовой). Примеры. (2 часа)

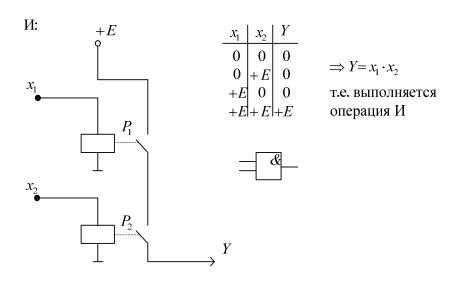

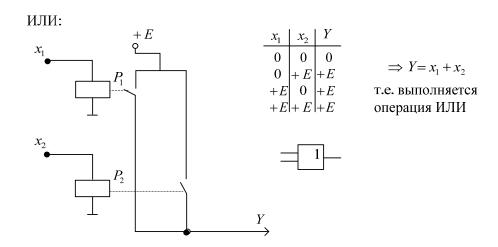

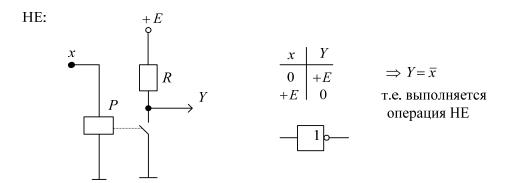

Лекция 5. Переход от алгебраической формы к структурной схеме и наоборот. Логические элементы (элементы И, ИЛИ, исключающее ИЛИ, НЕ). Функционально полные системы логических элементов. Наборы логических элементов И, ИЛИ, НЕ (И-НЕ, ИЛИ-НЕ). (2 часа)

Лекция 6. Минимизация Булевых функций. Карты Карно. Примеры реализации Булевых функций. (2 часа)

### Тема 3. Основы построения логических схем (12 часов)

Лекция 7. Импульсные сигналы: основные параметры и терминология. Электрический импульс (форма импульса, фронт импульса, срез импульса, длительность импульса, коэффициент заполнения, скважность). Ключевой режим. Ключевые схемы. (2 часа)

Лекция 8. Ключи на биполярных транзисторах. Транзисторные ключи: назначение, схемы, элементы. Схема с общим эмиттером. Схема с общим коллектором. Схема с общей базой. Достоинства и недостатки транзисторных ключей с различными схемами. (2 часа)

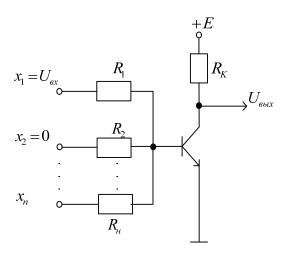

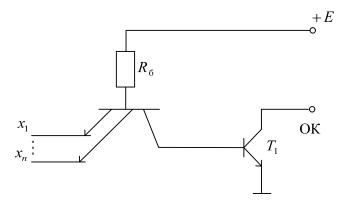

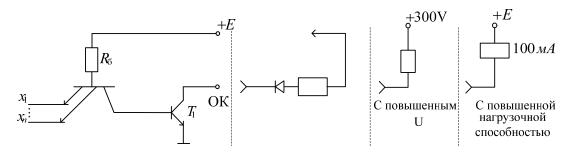

Лекция 9. Переходные процессы в ключах с общим эмиттером. Алгоритм расчета переходных характеристик. Ограничения быстродействия транзисторных ключей и приемы их исправления: использование в базе ускоряющих емкостей, ключ с ускоряющим диодом, ключ с диодом Шоттки. (2 часа) Лекция 10. Логические элементы на реле и переключателях. Физический эквивалент логической переменной. Логические схемы И, ИЛИ, НЕ. Резисторно-транзисторная логика (РТЛ): схема, таблица истинности, достоинства и недостатки. (2 часа)

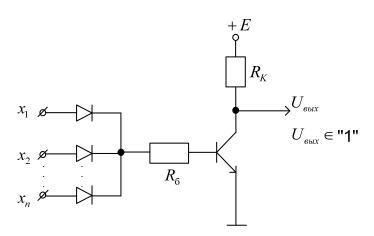

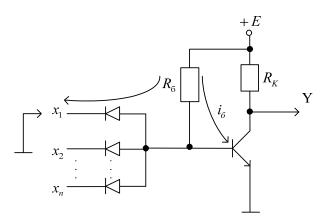

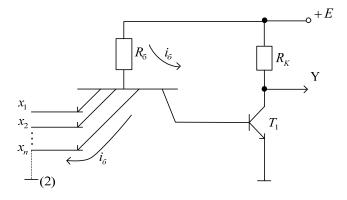

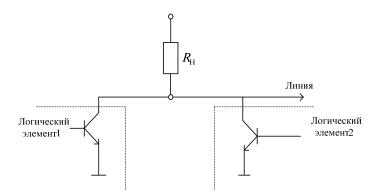

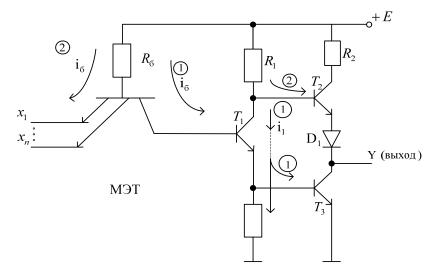

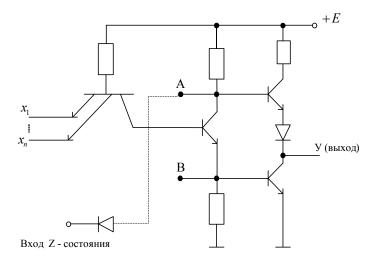

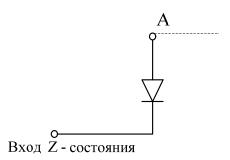

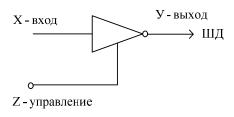

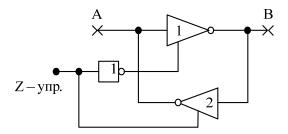

Лекция 11. Диодно-транзисторная логика (ДТЛ): базовые элементы, реализация логических элементов, преимущества перед РТЛ. Транзисторно-

транзисторная логика (ТТЛ). Построение логических элементов на базе ТТЛ. Элементы ТТЛ с разными выходными каскадами: элементы с открытым коллектором, элементы со сложным выходным каскадом, элементы с тремя состояниями на выходе. Шинный формирователь. (2 часа)

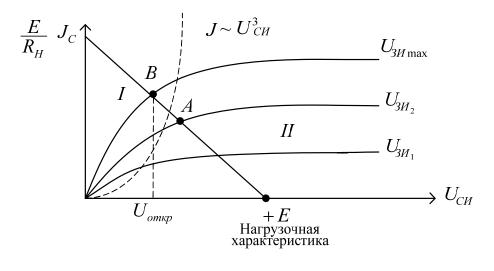

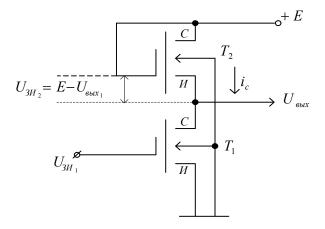

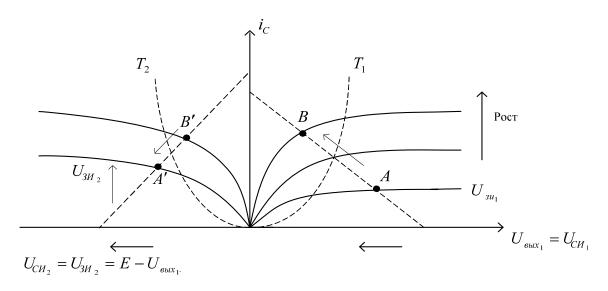

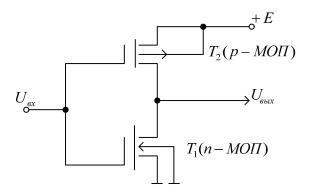

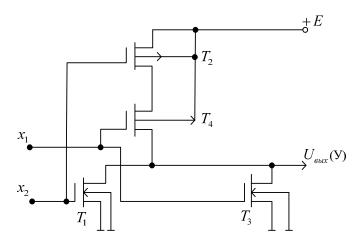

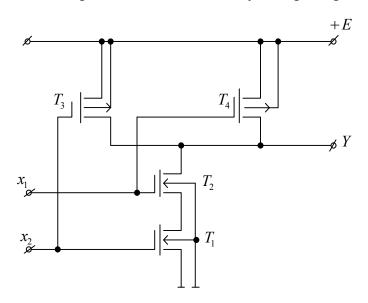

Лекция 12. Ключи на полевых транзисторах. Структура Металл-Окисел-Полупроводник (МОП). Ключ с динамической нагрузкой. Ключ на комплиментарных парах (КМОП-технология). Базовые элементы КМОП-логики. (2 часа)

### Тема 4. Основные узлы цифровых устройств. (12 часов)

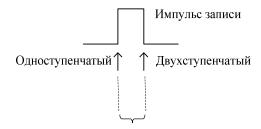

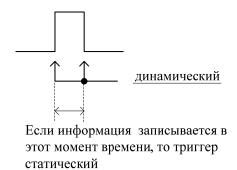

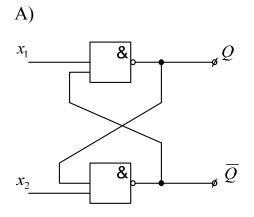

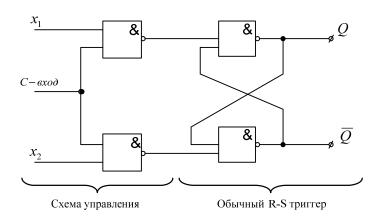

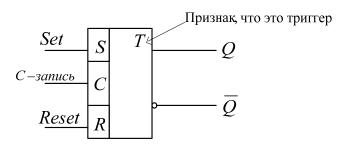

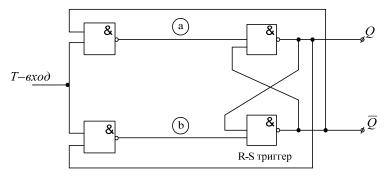

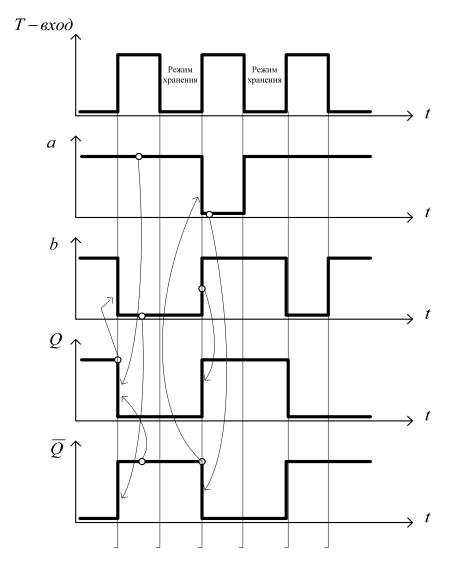

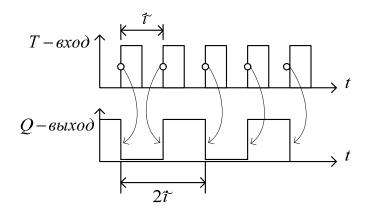

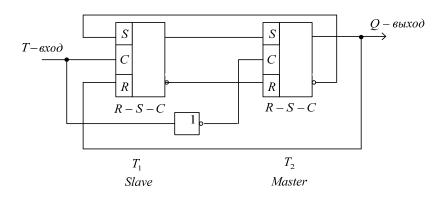

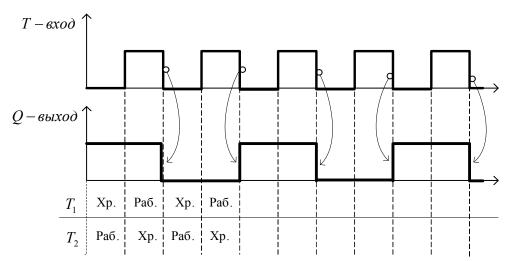

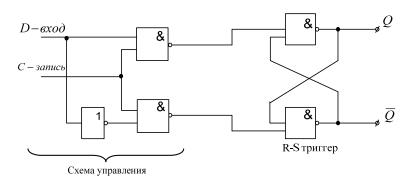

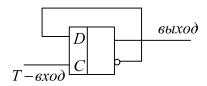

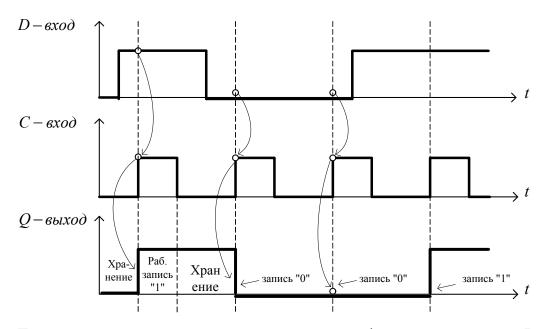

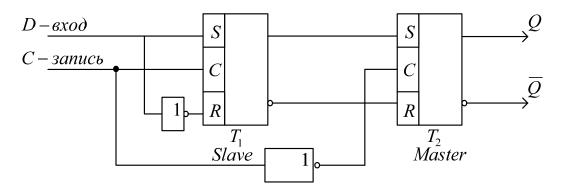

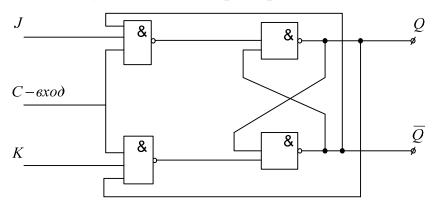

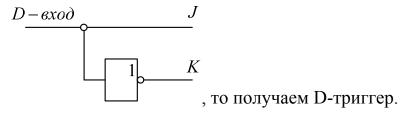

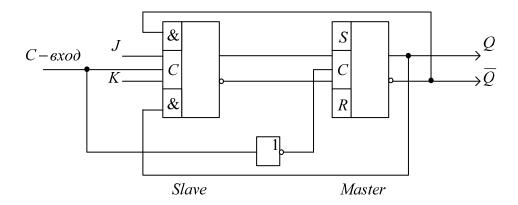

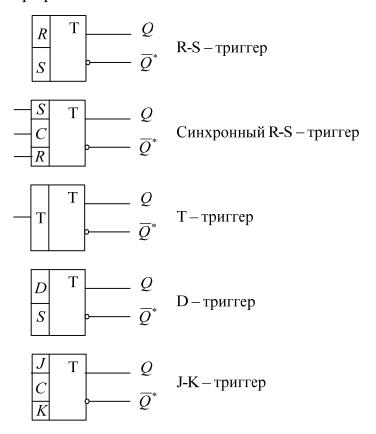

Лекция 13. Триггеры: назначение, характеристики, классификация. RS-триггеры. Т-триггеры (счетные триггеры). D-триггеры (триггеры задержки). JK-триггеры. Графические обозначения. (2 часа)

Лекция 14. RS-триггеры, синхронные RS-триггеры: схемотехника, таблица истинности. Запрещенное состояние. Триггеры на элементах ИЛИ-НЕ. (2 часа)

Лекция 15. Т-триггеры (одно- и двуступенчатые). Счетчики на Т-триггерах. D-триггеры (одно- и двуступенчатые). Счетчики на D-триггерах. ЈК-триггеры (одно- и двуступенчатые). (2 часа)

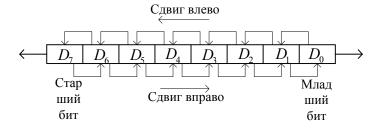

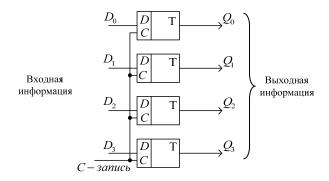

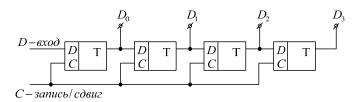

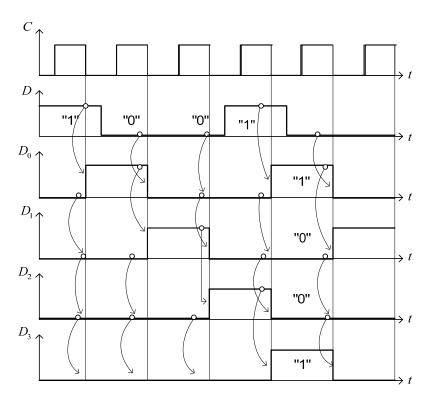

Лекция 16. Регистры: назначение и классификация. Регистры хранения. Сдвиговые регистры. Универсальные регистры. (2 часа)

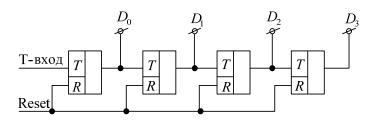

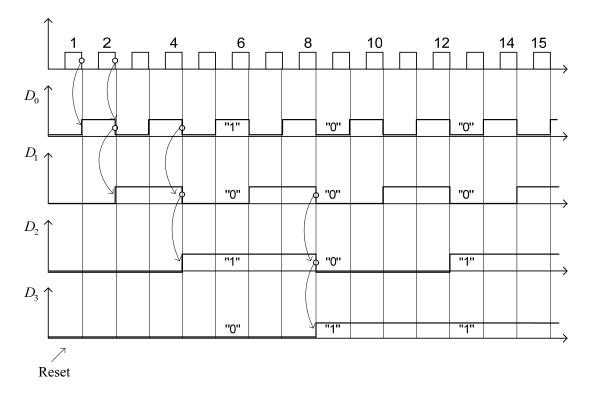

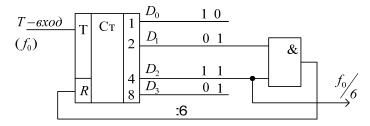

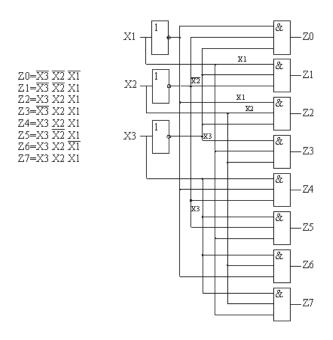

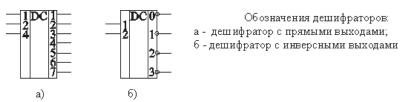

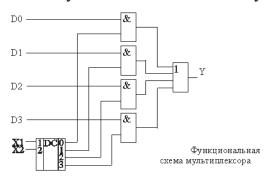

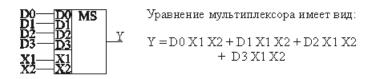

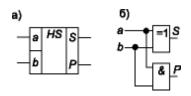

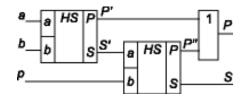

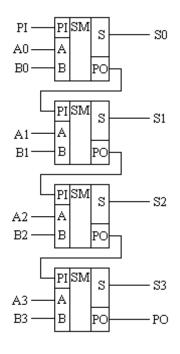

Лекция 17. Двоичные счетчики: назначение и классификация. Дешифраторы: классификация и назначение. Мультиплексоры. Сумматоры: назначение и классификация. Полусумматор. Полный сумматор. Многоразрядный сумматор. (2 часа)

Лекция 18. Устройства памяти на основе цифровых схем. Алгоритмы работы. Работа с шиной данных. Циклы чтения и записи памяти. (2 часа)

Конспекты лекций приводятся в Приложении 1.

## II. СТРУКТУРА И СОДЕРЖАНИЕ ПРАКТИЧЕСКОЙ ЧАСТИ КУРСА

Лабораторные работы (72 часа),

в т.ч. с использованием методов интерактивного/активного обучения - компьютерное моделирование (54 часа)

**Лабораторная работа 1.** Изучение характеристик интегральных логических элементов (8 час.)

Лабораторная работа 2. Синтез комбинационных логических схем (8 час.)

Лабораторная работа 3. Триггеры. Часть 1. (8 час.)

Лабораторная работа 4. Триггеры. Часть 2. (8 час.)

Лабораторная работа 5. Регистры (8 час.)

Лабораторная работа 6. Счетчики импульсов (8 час.)

Лабораторная работа 7. Изучение микросхем памяти (8 час.)

Лабораторная работа 8. Синтез цифровых автоматов. Часть 1. (8 час.)

Лабораторная работа 9. Синтез цифровых автоматов. Часть 2 (8 час.)

Содержание лабораторных работ приводится в приложении 2.

## III. УЧЕБНО-МЕТОДИЧЕСКОЕ ОБЕСПЕЧЕНИЕ САМОСТОЯТЕЛЬНОЙ РАБОТЫ ОБУЧАЮЩИХСЯ

Учебно-методическое обеспечение самостоятельной работы обучающихся по дисциплине «Цифровая электроника» представлено в Приложении 3 и включает в себя:

- план-график выполнения самостоятельной работы по дисциплине, в том числе примерные нормы времени на выполнение по каждому заданию;

- характеристика заданий для самостоятельной работы обучающихся и методические рекомендации по их выполнению;

- требования к представлению и оформлению результатов самостоятельной работы;

- критерии оценки выполнения самостоятельной работы.

## IV. КОНТРОЛЬ ДОСТИЖЕНИЯ ЦЕЛЕЙ КУРСА

| №   | Контролируемые разделы                       | Коды                       | и этапы             | Оценочн                          | ые средства                 |

|-----|----------------------------------------------|----------------------------|---------------------|----------------------------------|-----------------------------|

| п/п | / темы дисциплины                            |                            | ирования<br>етенций | текущий<br>контроль              | промежуточная<br>аттестация |

| 1   | Тема 1. Введение в курс цифровой электроники | ОПК-3                      | знает               | самостоя-<br>тельная рабо-<br>та | экзамен,<br>вопросы 1-4     |

|     |                                              |                            | умеет               | самостоя-<br>тельная рабо-<br>та | задание,<br>тип 1           |

|     |                                              |                            | владеет             | самостоя-<br>тельная рабо-<br>та | задание,<br>тип 1           |

| 2   | Тема 2. Основы теории логических схем        | ОПК-3,<br>ПК-13,           | знает               | самостоя-<br>тельная рабо-<br>та | экзамен,<br>вопросы 5-10    |

|     |                                              |                            | умеет               | самостоя-<br>тельная рабо-<br>та | задание,<br>тип 2           |

|     |                                              |                            | владеет             | самостоя-<br>тельная рабо-<br>та | задание,<br>тип 2           |

| 3   | Тема 3. Основы построения логических схем    | ОПК-3,<br>ПК-13,<br>ПК-20, | знает               | самостоя-<br>тельная рабо-<br>та | экзамен,<br>вопросы 11-18   |

|     |                                              | ПК-29                      | умеет               | самостоя-<br>тельная рабо-<br>та | задание,<br>тип 3           |

|     |                                              |                            | владеет             | самостоя-<br>тельная рабо-<br>та | задание,<br>тип 3           |

| 4   | Тема 4. Основные узлы цифровых устройств     | ОПК-3,<br>ПК-13,<br>ПК-20, | знает               | самостоя-<br>тельная рабо-<br>та | экзамен,<br>вопросы 19-32   |

|     |                                              | ПК-29                      | умеет               | самостоя-<br>тельная рабо-<br>та | задание,<br>тип 4           |

|     |                                              |                            | владеет             | самостоя-<br>тельная рабо-<br>та | задание,<br>тип 4           |

### Вопросы к экзамену

- 1. Двоичная переменная. Основные логические операции.

- 2. Основные теоремы Булевой алгебры. Теоремы с одной переменной.

- 3. Основные теоремы Булевой алгебры. Теоремы с двумя и более переменными.

- 4. Булевы функции. Словесный и табличный способы задания Булевых функций.

- 5. Алгебраический и числовой способы задания Булевых функций. Примеры.

- 6. Переход от алгебраической формы к логической схеме и наоборот. Примеры.

- 7. Функционально полные системы логических элементов.

- 8. Минимизация Булевых функций. Карты Карно. Примеры.

- 9. Импульсные сигналы. Основные определения и терминология.

- 10. Ключи на биполярных транзисторах.

- 11. Переходные процессы в ключах на биполярных транзисторах.

- 12. Способы увеличения быстродействия ключей на биполярных транзисторах.

- 13. Ключи на полевых транзисторах. Ключ с резистивной нагрузкой.

- 14. Ключи на полевых транзисторах. Ключ с нелинейной нагрузкой.

- 15. Логические элементы на переключателях и диодах.

- 16. Резистивно-транзисторная логика. Базовые элементы.

- 17. Диодно-транзисторная логика. Базовые элементы.

- 18. Транзисторно-транзисторная логика (ТТЛ). Базовые элементы ТТЛ.

- 19. Элементы ТТЛ со сложным выходным каскадом, с тремя состояниями.

- 20. КМОП-логика.

- 21. Общая характеристика, классификация триггеров. RS-триггеры.

- 22. Синхронные RS-триггеры. Т-триггеры.

- 23. D- и ЈК-триггеры.

- 24. D- и ЈК-триггеры в счетном режиме.

- 25. Классификация и назначение регистров. Регистры хранения. Примеры.

- 26. Сдвиговые и универсальные регистры. Примеры.

- 27. Классификация и назначение счетчиков.

- 28. Счетчики с произвольным коэффициентом деления.

- 29. Классификация и назначение шифраторов и дешифраторов.

- 30. Мультиплексоры.

- 31. Назначение, классификация сумматоров. Полусумматор.

- 32. Полный сумматор. Построение многоразрядных сумматоров.

Типовые контрольные задания, методические материалы, определяющие процедуры оценивания знаний, умений и навыков и (или) опыта деятельности, а также критерии и показатели, необходимые для оценки знаний, умений, навыков и характеризующие этапы формирования компетенций в процессе освоения образовательной программы, представлены в Приложении 4.

## V. СПИСОК УЧЕБНОЙ ЛИТЕРАТУРЫ И ИНФОРМАЦИОННО-МЕТОДИЧЕСКОЕ ОБЕСПЕЧЕНИЕ ДИСЦИПЛИНЫ

### Основная литература

(электронные и печатные издания)

- 1. Янсен, И. Курс цифровой электроники. Т. 1, 2, 3. / И. Янсен. М.: Мир, 1987. 343 с. Режим доступа: ЭБС twirpx.com, https://www.twirpx.com/file/1366595/

- 2. Гусев, В.В. Основы импульсной и цифровой техники / В.В. Гусев. М.: Советская школа, 1975. 467 с. Режим доступа: ЭБС twirpx.com, <a href="http://znanium.com/go.php?id=473097">http://znanium.com/go.php?id=473097</a>

- 3. Титце, У. Полупроводниковая схемотехника: Справочное руководство. / У. Титце, К. Шенк. М.: Мир, 1982. 512 с. Режим доступа: ЭБС IPRbooks http://www.iprbookshop.ru/15854

- 4. Хоровиц П. Искусство схемотехники: В 3-х томах: Т.1,2,3. Пер. с англ. / П. Хоровиц, У. Хилл. М.: Мир, 1983. 367 с. Режим доступа: ЭБС IPRbooks <a href="http://www.iprbookshop.ru/22438">http://www.iprbookshop.ru/22438</a>

- 5. Основы цифровой электроники: [Электронный ресурс]: учебное пособие для высших учебных заведений. / Интернет Электрон. Дан. Режим доступа: ЭБС RBTL.RU http://www.rbtl.ru/wsap/posobie/

- 6. Смирнова, Г.Н. Проектирование экономических информационных систем: учебник / Г.Н. Смирнова, А.А. Сорокин, Ю.Ф. Тельнов; под ред. Ю.Ф. Тельнова. 2-е изд. М.: Финансы и статистика, 2007. 512 с. ЭК НБ ДВФУ: <a href="http://lib.dvfu.ru:8080/lib/item?id=chamo:258116&theme=FEFU">http://lib.dvfu.ru:8080/lib/item?id=chamo:258116&theme=FEFU</a>

- 7. Соловьев, И.В. Проектирование информационных систем. Фундаментальный курс.: учеб. пособие / И.В. Соловьев, А.А. Майоров ; под ред. В.П. Савиных. М.: Академический проект, 2009. 398 с. ЭК НБ ДВФУ: <a href="http://lib.dvfu.ru:8080/lib/item?id=chamo:295823&theme=FEFU">http://lib.dvfu.ru:8080/lib/item?id=chamo:295823&theme=FEFU</a>

### Дополнительная литература

(печатные и электронные издания)

- 1. Вендров, А.М. Проектирование программного обеспечения экономических информационных систем: учебник / А.М. Вендров. 2-е изд. М.: Финансы и статистика, 2005. 544 с.

- ЭК НБ ДВФУ: <a href="http://lib.dvfu.ru:8080/lib/item?id=chamo:247734&theme=FEFU">http://lib.dvfu.ru:8080/lib/item?id=chamo:247734&theme=FEFU</a>

- 2. Грекул, В.И. Управление внедрением информационных систем : учеб. пособие [Электронный ресурс] / В.И. Грекул, Г.Н. Денищенко, Н.Л. Коровкина. М.: Интернет-Ун-т Информ. технологий, 2008. 224 с. Режим доступа: ЭБС IPRbooks <a href="http://www.iprbookshop.ru/16102">http://www.iprbookshop.ru/16102</a>

- 3. Избачков, Ю.С. Информационные системы: учебник для вузов / Ю. Избачков, В. Петров, А. Васильев, И. Телина. 3-е изд. СПб. : Питер, 2011. 544 с.

- ЭК НБ ДВФУ: http://lib.dvfu.ru:8080/lib/item?id=chamo:340811&theme=FEFU

4. Калянов, Г.Н. Моделирование, анализ, реорганизация и автоматизация бизнес-процессов : учеб. пособие для вузов / Г.Н. Калянов. – М.: Финансы и статистика, 2006. – 240 с.

ЭК НБ ДВФУ: http://lib.dvfu.ru:8080/lib/item?id=chamo:235258&theme=FEFU

5. Скрипкин, К.Г. Экономическая эффективность информационных систем [Электронный ресурс] / К.Г. Скрипкин. — М.: ДМК Пресс, 2009. — 256 с. — Режим доступа: ЭБС IPRbooks <a href="http://www.iprbookshop.ru/7635">http://www.iprbookshop.ru/7635</a>

### Нормативно-правовые материалы

- 1. ГОСТ 34.003-90. Информационная технология. Комплекс стандартов на автоматизированные системы. Автоматизированные системы. Термины и определения [Текст]. Взамен ГОСТ 34.003-84, ГОСТ 22487-77 Введ. 1992-01-01. М.: Изд-во стандартов, 1997: <a href="http://www.internet-law.ru/gosts/gost/10673/">http://www.internet-law.ru/gosts/gost/10673/</a>

- 2. ГОСТ 34.201-89. Виды, комплектность и обозначение документов при создании автоматизированных систем [Текст]. Введ. 1990-01-01. М.: Изд-во стандартов, 1997: <a href="http://www.internet-law.ru/gosts/gost/11319/">http://www.internet-law.ru/gosts/gost/11319/</a>

- 3. ГОСТ 34.601-90. Информационная технология. Комплекс стандартов на автоматизированные системы. Автоматизированные системы. Стадии создания [Текст]. Взамен ГОСТ 24.601-86, ГОСТ 24.602-86. Введ. 1990-29-12. М.: Изд-во стандартов, 1997: <a href="http://www.internet-law.ru/gosts/gost/10698/">http://www.internet-law.ru/gosts/gost/10698/</a>

- 4. ГОСТ 34.602-89. Информационная технология. Комплекс стандартов на автоматизированные системы. Автоматизированные системы. Техническое задание на создание автоматизированной системы [Текст]. Взамен ГОСТ 24.201-85. Введ. 1990-01-01. М.: Изд-во стандартов, 1997: <a href="http://www.internet-law.ru/gosts/gost/11254/">http://www.internet-law.ru/gosts/gost/11254/</a>

- 5. ГОСТ 34.603-92. Информационная технология. Комплекс стандартов на автоматизированные системы. Автоматизированные системы. Виды испытаний автоматизированных систем [Текст]. Введ. 1993-01-01. М.: Изд-во стандартов, 1991: <a href="http://www.internet-law.ru/gosts/gost/12467/">http://www.internet-law.ru/gosts/gost/12467/</a>

- 6. ГОСТ Р ИСО/МЭК 12207-2010. Информационная технология. Системная и программная инженерия. Процессы жизненного цикла программных средств [Текст]. Введ. 2012-01-03. М.: Стандартинформ, 2011: <a href="http://protect.gost.ru/v.aspx?control=8&baseC=-1&page=0&month=-1&year=-1&search=&RegNum=1&DocOnPageCount=15&id=169094">http://protect.gost.ru/v.aspx?control=8&baseC=-1&page=0&month=-1&year=-1&search=&RegNum=1&DocOnPageCount=15&id=169094</a>

- 7. ГОСТ Р ИСО/МЭК ТО 15271-2002. Информационная технология. Руководство по применению ГОСТ Р ИСО/МЭК 12207 (Процессы жизненного цикла программных средств) [Текст]. Введ. 2002-05-06. М.: Изд-во стандартов, 2002: <a href="http://www.internet-law.ru/gosts/gost/6430/">http://www.internet-law.ru/gosts/gost/6430/</a>

# Перечень ресурсов информационно-телекоммуникационной сети «Интернет»

- 1. Государственная программа «Информационное общество» (2011–2020 годы): http://minsvyaz.ru/ru/activity/programs/1/

- 2. Информационное общество. Информационный сайт: <a href="http://infdeyatchel.narod.ru/inf\_ob.htm">http://infdeyatchel.narod.ru/inf\_ob.htm</a>

- 3. Корпоративная информационная система: определение и структура. Современные подходы к построению корпоративных информационных систем. Образовательный портал: <a href="http://e-educ.ru/ism14.html">http://e-educ.ru/ism14.html</a>

- 4. Корпоративные информационные системы. Портал «Корпоративный менеджмент». Библиотека управления, статьи и пособия: <a href="http://www.cfin.ru/software/kis/">http://www.cfin.ru/software/kis/</a>

# VI. МЕТОДИЧЕСКИЕ УКАЗАНИЯ ПО ОСВОЕНИЮ ДИСЦИПЛИНЫ

Общая трудоемкость дисциплины составляет 180 час. (5 ЗЕ). Аудиторные занятия составляют 108 час. в виде лекций (36 час.) и лабораторных работ (72 час.).

По дисциплине предусмотрена самостоятельная работа в объеме 72 час. Рекомендуется учащимся планировать внеаудиторную самостоятельную работу в объеме 3,5 часа в учебную неделю.

Для углубленного изучения теоретического материала курса дисциплины рекомендуются использовать основную и дополнительную литературу, указанную в приведенном выше перечне.

Рекомендованные источники доступны обучаемым в научной библиотеке (НБ) ДВФУ (в перечне приведены соответствующие гиперссылки этих источников), а также в электронных библиотечных системах (ЭБС), с доступом по гиперссылкам — ЭБС twirpx.com, ЭБС издательства "Лань" (http://e.lanbook.com/), ЭБС Znanium.com НИЦ "ИНФРА-М" (http://znanium.com/), ЭБС IPRbooks (http://iprbookshop.ru/) и другие ЭБС, используемые в ДВФУ<sup>1</sup>.

## VII. МАТЕРИАЛЬНО-ТЕХНИЧЕСКОЕ ОБЕСПЕЧЕНИЕ ДИСЦИПЛИНЫ

Для проведения исследований, связанных с выполнением задания по практике, а также для организации самостоятельной работы студентам доступно следующее лабораторное оборудование и специализированные кабинеты, соответствующие действующим санитарным и противопожарным нормам, а также требованиям техники безопасности при проведении учебных и научно-производственных работ:

| Наименование оборудованных      | Перечень основного оборудования               |

|---------------------------------|-----------------------------------------------|

| помещений и помещений для       |                                               |

| самостоятельной работы          |                                               |

| Владивосток, о. Русский, п.     | Мультимедийное оборудование:                  |

| Аякс д.10, корпус L, ауд. L 565 | ЖК-панель 47", Full HD, LG M4716 CCBA - 1 шт. |

| учебная аудитория для проведе-  | Парты и стулья                                |

| ния занятий лекционного типа,   |                                               |

| занятий семинарского типа,      |                                               |

| групповых и индивидуальных      |                                               |

| консультаций, текущего кон-     |                                               |

| троля и промежуточной атте-     |                                               |

| стации                          |                                               |

<sup>&</sup>lt;sup>1</sup> https://www.dvfu.ru/library/electronic-resources/

-

| D                               | 7 4                                                 |

|---------------------------------|-----------------------------------------------------|

| Владивосток, о. Русский, п.     | 7 4-х канальных цифровых модулей визуализации       |

| Аякс д.10, корпус L, ауд. L 503 | сигналов, 2 циф, осциллографа С1-65, 2-х каналь-    |

| специализированная лаборато-    | ный модуль цветной визуализации сигна-              |

| рия кафедры КС: Лаборатория     | лов:Осциллограф TDS-3012B, 6 2-х канальных          |

| радиотехники и радиоэлектро-    | цифровых модулей визуализации сигналов с изоли-     |

| ники                            | рованными вх.TPS-2012, 2-х канальный формирова-     |

|                                 | тель сигналов произвольной формы: Генератор         |

|                                 | AFG-3022, широкополосный формирователь сигна-       |

|                                 | лов произвольной формы:Генератор AFG-3101, про-     |

|                                 | граммируемый источник питания постоянного тока      |

|                                 | LPS-304, столы лабораторные и стулья                |

| Читальные залы Научной биб-     | Моноблок HP РгоОпе 400 All-in-One 19,5              |

| лиотеки ДВФУ с открытым до-     | (1600x900), Core i3-4150T, 4GB DDR3-1600            |

| ступом к фонду (корпус А -      | (1x4GB), 1TB HDD 7200 SATA, DVD+/-                  |

| уровень 10)                     | RW,GigEth,Wi-Fi,BT,usb kbd/mse,Win7Pro (64-         |

| Учебная аудитория для прове-    | bit)+Win8.1Pro(64-bit),1-1-1 Wty Скорость доступа в |

| дения самостоятельной работы    | Интернет 500 Мбит/сек. Рабочие места для людей с    |

|                                 | ограниченными возможностями здоровья оснащены       |

|                                 | дисплеями и принтерами Брайля; оборудованы: пор-    |

|                                 | тативными устройствами для чтения плоскопечат-      |

|                                 | ных текстов, сканирующими и читающими маши-         |

|                                 | нами видеоувелечителем с возможностью регуляции     |

|                                 | цветовых спектров; увеличивающими электронны-       |

|                                 | ми лупами и ультразвуковыми маркировщиками          |

В целях обеспечения специальных условий обучения инвалидов и лиц с ограниченными возможностями здоровья в ДВФУ все здания оборудованы пандусами, лифтами, подъемниками, специализированными местами, оснащенными туалетными комнатами, табличками информационнонавигационной поддержки.

### МИНИСТЕРСТВО ОБРАЗОВАНИЯ И НАУКИ РОССИЙСКОЙ ФЕДЕРАЦИИ

Федеральное государственное автономное образовательное учреждение высшего профессионального образования

# «Дальневосточный федеральный университет» (ДВФУ)

### ШКОЛА ЕСТЕСТВЕННЫХ НАУК

### КОНСПЕКТ ЛЕКЦИЙ

# по дисциплине «Цифровая электроника» Направление подготовки 09.03.02 Информационные системы и технологии

профиль «Информационные системы и технологии в связи» **Форма подготовки очная**

Владивосток 201

### **ВВЕДЕНИЕ**

Электронная промышленность наиболее стремительно начала развиваться в середине прошлого века. С 60-х годов прошлого столетия и до настоящего времени средний годовой темп роста электронной промышленности составил не менее 17%, и на сегодня потенциал развития отрасли далеко не исчерпан. Такого роста не было ни в одной другой отрасли развития мировой промышленности.

Главной движущей силой рынка электроники была и остается полупроводниковая технология. Повышение производительности, миниатюризация и снижение стоимости полупроводниковых приборов всегда вызывали появление новых отраслей применения, которое обеспечивало кратное увеличение спроса на электронные компоненты и рост мирового рынка электроники в целом. Так, в 70-х годах прошлого столетия этим применением было телевидение, а с середины 80-х - компьютер, в 90-х - Интернет и цифровые системы связи, затем совершенно новое приложение успехов цифровой электроники сотовая и спутниковая связь. Важная для электронной отрасли проблема — это дефицит кадров, которая является актуальной и в настоящее время. Большинство производителей электронного оборудования обеспокоено недостатком квалифицированных специалистов, поэтому и в 21 веке изучение цифровой электроники общепризнанно является чрезвычайно актуальной и до конца не решенной проблемой.

Настоящий курс лекций "Цифровая электроника" читается студентам четвертого курса факультета информационных технологий Института физики и информационных технологий Дальневосточного государственного университета для специальностей "Информационные системы и технологии" и "Компьютерная безопасность". По данному курсу в библиотеках и читальных залах университета имеется достаточное количество литературы, но на данный момент ни одна из них в полном объеме не соответствует программе, содержащейся в государственных образовательных стандартах второго поколения. Чтобы полностью восполнить образовавшийся пробел и обеспечить

студентов методическими материалами была поставлена цель оформить методические указания в виде конспекта лекций, которые уже более двадцати пяти лет читаются студентам данных специальностей.

# Глава 1. Основы теории построения логических схем §1.1 Логические высказывания. Двоичная переменная. Системы счисления

Теория построения современных логических или цифровых устройств опирается на основные логические высказывания, сформулированные еще в середине IX века английским ученым Дж. Булем. Именно он сформулировал основные положения булевой алгебры, которая полностью опирается на дво-ичную переменную и, основы которой, спустя почти сто лет, были реализованы на практике в виде первых цифровых устройств.

Буль ввел двоичную переменную исходя из следующих высказываний: если не ложь, то истина (правда); если не правда (истина), то ложь.

Введем некоторую двоичную переменную **x**, которая в высказываниях может принимать только два значения - «ложь» или «правда», или в математических символах, например, значения 0 или 1. Тогда сформулированные Булем высказывания можно математически и логически описать следующим образом:

### Операция **ИЛИ (OR)** [дизьюнкция]

- 0 + 0 = 0 ложь или ложь есть ложь;

- 0 + 1 = 1 ложь или правда есть правда;

- 1 + 0 = 1 правда или ложь есть правда;

- 1 + 1 = 1 правда или правда есть правда.

### Операция **И** (**AND**) [коньюнкция]

- $0 \cdot 0 = 0$  ложь и ложь есть ложь;

- $0 \cdot 1 = 0$  ложь и правда есть ложь;

- $1 \cdot 0 = 0$  правда и ложь есть ложь;

$1 \cdot 1 = 1$  — правда и правда есть правда.

Где,

$$\mathbf{x} \in \left\{ \begin{array}{c} \text{ложь,} & 0 \\ \end{array} \right\}$$

правда, 1

### Операция отрицания или инверсии (или операция НЕ)

Если  $\mathbf{x} \neq \mathbf{0}$ , то  $\mathbf{x} = 1$ ; не ложь есть правда;

Если  $\mathbf{x} \neq 1$ , то  $\mathbf{x} = 0$ ; не правда есть ложь.

Практическое использование данных высказываний в вычислительных системах позволило сформулировать еще одно логическое высказывание, которое по значимости не уступает ранее введенным Булем, а именно:

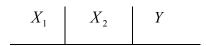

### Операция исключающее ИЛИ (XOR)

Данное высказывание применимо только к двум двоичным переменным  $\chi_1$ ,  $\chi_2$ и с помощью таблицы истинности означает следующее:

| $X_1$ | $X_2$ | у |

|-------|-------|---|

| 0     | 0     | 0 |

| 0     | 1     | 1 |

| 1     | 0     | 1 |

| 1     | 1     | 0 |

Рассмотренные выше логические высказывания оказались наиболее подходящими для организации вычислений и другой математической обработки в рамках двоичной системы счисления. Если по аналогии с алфавитом букв ввести алфавит цифр, то под *системой счисления* понимают совокупность правил и принятый алфавит цифр для подсчета количества чего – либо.

Системы счисления создавались в процессе эволюции человечества исходя из удобства записи и их практического использования и, по мнению большинства исследователей, имели следующие предпосылки для своего происхождения:

1. Анатомического происхождения, то есть когда для подсчета чего–либо люди использовали особенности строения организма человека, это такие,

как: пятеричная, десятеричная, двенадцатеричная, двадцатеричная. Очевидно, что для этих систем основанием послужили количественные характеристики конечностей человека.

- 2. <u>Алфавитного происхождения</u>: для отображения чего—либо используется уже существующий алфавит, к значкам которого добавляется определенный символ (знак), например, значок «тильда».

- 3. <u>Машинные системы счисления</u> сформировались в процессе развития цифровой техники. Они включают в себя такие, как:

- Двоичную, алфавит цифр состоит из символов {0,1};

- восьмеричную {0,1,2,3,4,5,6,7};

- шестнадцатеричную {0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F}

Цифровая электроника работает только в рамках двоичной системы счисления.

Адресное пространство удобно в шестнадцатеричной системе счисления.

4. <u>Прочие системы счисления</u> (обычно римская и вавилонская). Для таких систем принято использовать ограниченное количество символов, подсчет количества которых и определяет количество чего-либо.

Независимо от происхождения, все системы счисления подразделяются на *позиционные* и *непозиционные*.

В *позиционных системах счисления* каждый символ из алфавита цифр несет двойную нагрузку: с одной стороны позиция отображает вес, порядок или разряд числа, с другой стороны – указывает на количество чего—либо. Это позволяет любое число формализовать, т.е. представить в следующем виде: <число $> = \sum_{i=0}^{m-1} \chi_i b^i$ , где  $\chi_i$  - символ из алфавита цифр;

b – основание;

i — номер позиции справа-налево;

*m* – количество разрядов при написании числа.

Данное выражение является основой для организации вычислений с помощью электронно-вычислительных машин.

Например:

$$1023_{10} = 3.10^{0} + 2.10^{1} + 0.10^{2} + 1.10^{3}$$

$110011_{2} = 1.2^{0} + 1.2^{1} + 0.2^{2} + 0.2^{3} + 1.2^{4} + 1.2^{5} = 51_{10}$

К *непозиционным системам счисления* относят такие, где правила вычислений формализовать нельзя (например, римская):

$$IV = V - I$$

$$VIII = V + I + I + I$$

$$XI = X + I$$

Таким образом, в вычислительной технике возможно использование только позиционные системы счисления, а применительно к булевой алгебре, такой системой счисления является двоичная система счисления.

### § 1.2 Основные теоремы Булевой алгебры

Теоретической основой для построения логических схем является Булева алгебра, работа с которой опирается на основные теоремы. Они сформулированы для двоичной переменной, которая обычно обозначается символами латинского алфавита и может принимать только одно из двух значений 0 или 1:

$$X,Y,Z,...,A,B,C,D,E \in \{0,1\}.$$

Как правило, теоремы Булевой алгебры доказываются либо простым перебором, либо с помощью ранее сформулированных теорем. Все основные теоремы сгруппированы по двум категориям:

а) с одной переменной (x), к которым относят:

$$x + 0 = x$$

$$x + x = x$$

$$x + 1 = 1$$

$$x + \overline{x} = 1$$

$$x \cdot 0 = 0$$

$$x \cdot x = x$$

$$x \cdot 1 = x$$

$$x \cdot \overline{x} = 0$$

$$= x = x$$

б) теоремы с двумя и более переменными:

1. Переместительный закон:

$$\begin{cases} x + y = y + x \\ xy = yx \end{cases}$$

2. Сочетательный закон:

$$x + y + z = x + (y + z) = (x + y) + z = (x + z) + y$$

$$xyz = y(xz) = x(yz) = z(xy)$$

3. Распределительный закон:

$$x(y+z) = xy + xz$$

$$xy + z = (x+z)(y+z)$$

Доказательство: раскроем скобки

$$(x+z) \cdot (y+z) = xy + zy + xz + zz = xy + z(y+x+1) = xy + z \cdot 1 = xy + z$$

4. Закон поглошения:

$$x + xy = x \rightarrow x \cdot 1 + xy = x(1+y) = x$$

$$x(x+y) = x \rightarrow x \cdot x + x \cdot y = x + xy \rightarrow x$$

5.

$$(x + y) \cdot y = xy \rightarrow xy + yy = xy$$

$xy + y = x + y \rightarrow x(y + y) + y = xy + xy + y = xy + y(x + 1) = xy + y$

6. Закон склеивания:

$$xy + xy = y \to y(x + x) = y (x + y) \cdot (x + y) = y \to xx + xy + yx + yy = y(x + x + y) = y$$

6. Теорема Де Моргана:

$$\overline{x+y+z+\dots} = \overline{x} \cdot \overline{y} \cdot \overline{z} \cdot \dots$$

$$\overline{xyz} = \overline{x} + \overline{y} + \overline{z} + \dots$$

С помощью данной теоремы можно осуществить переход от одной логической операции к другой.

Данная возможность играет существенную роль при изготовлении логических устройств, а именно существует возможность создания функционально полной системы логических элементов с помощью только одного по функциональности логического элемента, что технологически очень удобно. Доказательство теоремы Де-Моргана приведем на примере двух переменных, построив таблицы истинности для левой и правой частей выражения:

$$\overline{x+y} = \overline{x} \cdot \overline{y}$$

Таблица истинности для левой части выражения будет выглядеть следующим образом:

| х | У | x + y | $\overline{x+y}$ |

|---|---|-------|------------------|

| 0 | 0 | 0     | 1                |

| 0 | 1 | 1     | 0                |

| 1 | 0 | 1     | 0                |

| 1 | 1 | 1     | 0                |

Таблица истинности для правой части выражения будет выглядеть следующим образом:

| x | У | $\bar{x}$ | $\overline{y}$ | $\overline{x} \cdot \overline{y}$ |

|---|---|-----------|----------------|-----------------------------------|

| 0 | 0 | 1         | 1              | 1                                 |

| 0 | 1 | 1         | 0              | 0                                 |

| 1 | 0 | 0         | 1              | 0                                 |

| 1 | 1 | 0         | 0              | 0                                 |

Рассмотрим выражение:  $\overline{x \cdot y} = \overline{x} + \overline{y}$ . Таблица истинности для левой части:

| x | У | $x \cdot y$ | $\overline{x \cdot y}$ |

|---|---|-------------|------------------------|

| 0 | 0 | 0           | 1                      |

| 0 | 1 | 0           | 1                      |

| 1 | 0 | 0           | 1                      |

| 1 | 1 | 1           | 0                      |

Таблица истинности для правой части выражения будет выглядеть следующим образом:

| x | У | $\bar{x}$ | $\overline{y}$ | $\overline{x} + \overline{y}$ |

|---|---|-----------|----------------|-------------------------------|

| 0 | 0 | 1         | 1              | 1                             |

| 0 | 1 | 1         | 0              | 1                             |

| 1 | 0 | 0         | 1              | 1                             |

| 1 | 1 | 0 | 0 | 0 |

|---|---|---|---|---|

|   |   |   |   |   |

Сопоставляя значения в таблицах для левой и правой частей выражений получаем тождество, что и требовалось доказать.

### § 1.3 Булевы функции. Способы задания Булевых функций

Все логические схемы, используемые в цифровой электронике, являются прямой реализацией той или иной Булевой функции, то есть прежде чем сконструировать такое устройство, его необходимо сначала математически описать. Это математическое описание всегда начинается с построения Булевых функций, т.е. для определенной комбинации двоичных переменных задается значение Булевых функций.

Задать Булеву функцию – это указать, при каких комбинациях переменных она равна 0, а при каких равна 1.

F = F(A,B,C,...), где A,B,C,... - аргументы функции  $\in \{0,1\}$ ;

F – результат или сама функция также  $\in \{0,1\}$ .

Каждую комбинацию аргументов называют *набором*. Каждому набору присваивается номер. Общепринято номер набора считать равным числу, отображаемому в скобках двоичными переменными.

Пример: набор равен 5 (n=5)

Описываем функцию F для набора: F=F(1,0,1); (A,C = 1, B = 0).

Если функция задана во всех наборах, то такую функцию называют *полностью определенной*. Если функция задана только в части наборов, то ее называют *недоопределенной* (или факультативной).

Факультативными называют условия, когда для неопределенных наборов ее можно задать по своему усмотрению. Когда функция задана, дальнейшие ее преобразования опираются на основные теоремы Булевой алгебры.

Порядок выполнения логических операций в конечном выражении полностью соответствует принятому в классической алгебре, за следующими двумя исключениями:

- а) Если инверсия только над одной переменной, то она всегда выполняется первой;

- б) Если инверсия над алгебраическим выражением, то она выполняется в рамках данного приложения последней.

При этом знак равенства указывает только на то, что левые и правые части от него тождественны.

Существуют следующие способы задания Булевых функций:

- 1. Словесный (описательный) способ функция задается в виде текста. Пример: F(A,B,C)=1, если аргументы в данном наборе имеют нечетное количество единиц (или если два любых аргумента функции равны 0).

- 2. *Табличный* способ задания Булевой функции строится таблица истинности, в которой указываются номера наборов, соответствующее состояние аргументов и значение самой функции для каждого набора.

Например: зададим табличным способом Булеву функцию из трех аргументов, которая принимает значение единицы при четном значении нулей аргументов:

| <u>No</u> | A | В | C | F |

|-----------|---|---|---|---|

| набора    |   |   |   |   |

| 0         | 0 | 0 | 0 | 0 |

| 1         | 0 | 0 | 1 | 1 |

| 2         | 0 | 1 | 0 | 1 |

| 3         | 0 | 1 | 1 | 0 |

| 4         | 1 | 0 | 0 | 1 |

| 5         | 1 | 0 | 1 | 0 |

| 6         | 1 | 1 | 0 | 0 |

| 7         | 1 | 1 | 1 | 1 |

Пример: построим табличным способом Булевы функции управления семисегментным индикатором для трех входных аргументов (двоичных переменных). При этом примем во внимание, что если сигнал, поступающий на

сегмент равен логической единице, то сегмент горит, при логическом нуле – погашен.

Семисегментный индикатор представляет собой набор сегментов, геометрически расположенных относительно друг друга следующим образом:

Таблица Булевых функций управления семисегментным индикатором:

| <i>№</i><br>набора | Переменные |       | Булевы функции |   |   |   |   |   |   |   |

|--------------------|------------|-------|----------------|---|---|---|---|---|---|---|

| наоора             | $X_1$      | $X_2$ | $X_3$          | a | b | c | d | e | f | g |

| 0                  | 0          | 0     | 0              | 1 | 1 | 1 | 1 | 1 | 0 | 1 |

| 1                  | 0          | 0     | 1              | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| 2                  | 0          | 1     | 0              | 1 | 1 | 0 | 1 | 1 | 1 | 0 |

| 3                  | 0          | 1     | 1              | 1 | 1 | 1 | 1 | 0 | 1 | 0 |

| 4                  | 1          | 0     | 0              | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| 5                  | 1          | 0     | 1              | 1 | 0 | 1 | 1 | 0 | 1 | 1 |

| 6                  | 1          | 1     | 0              | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 7                  | 1          | 1     | 1              | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

Таким образом, задано сразу семь Булевых функций, которые зависят от общих трех элементов.

Алгебраический способ задания Булевых функций

Исходным для такого способа является табличное задание Булевых функций. Аналогичная форма необходима для перехода к структурной схеме, для минимизации Булевой функции с целью последующего размещения цифрового устройства на кристалле. Существуют два варианта задания функции алгебраическим способом:

1. Нормальная дизъюнктивная форма или задание Булевых функций по единицам.

Алгоритм задания следующий: из таблицы выбираются номера наборов, где функция равна 1, и строится сумма элементарных произведений этих наборов, при этом если переменная равна 0, то она берется с инверсией (элементарное произведение - произведение всех переменных для данного набора).

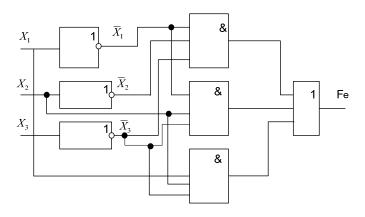

Зададим функцию  $f_e$  и  $f_g$ :

$$f_e = \overline{X}_1 \cdot \overline{X}_2 \cdot \overline{X}_3 + \overline{X}_1 \cdot X_2 \cdot \overline{X}_3 + X_1 \cdot X_2 \cdot \overline{X}_3$$

Все, функция задана алгебраическим способом.

$$f_{\mathrm{g}} = \ \overline{X}_{\mathrm{1}} \cdot \overline{X}_{\mathrm{2}} \cdot \overline{X}_{\mathrm{3}} + X_{\mathrm{1}} \cdot \overline{X}_{\mathrm{2}} \cdot \overline{X}_{\mathrm{3}} + X_{\mathrm{1}} \cdot \overline{X}_{\mathrm{2}} \cdot \overline{X}_{\mathrm{3}} + X_{\mathrm{1}} \cdot \overline{X}_{\mathrm{2}} \cdot \overline{X}_{\mathrm{3}}$$

2. Нормальная конъюнктивная форма (или задание Булевых функций по нулям).

Из таблицы выбираются наборы, где функция равна 0 и строиться произведение элементарных сумм для этих наборов. Если переменная равна 1, то она берется с инверсией. (Элементарная сумма – сумма всех переменных для данного набора).

Например, зададим  $f_a$  и  $f_d$ :

$$\begin{split} f_{a} &= (X_{4} + X_{2} + X_{3}) \cdot (X_{4} + X_{2} + X_{3}) \\ f_{d} &= (X_{4} + X_{2} + X_{3}) \cdot (X_{4} + X_{2} + X_{3}) \\ f_{d} &= (X_{4} + X_{2} + X_{3}) \cdot (X_{4} + X_{2} + X_{3}) \cdot (X_{4} + X_{2} + X_{3}) \cdot (X_{4} + X_{2} + X_{3}) \\ &= (X_{4} + X_{2} + X_{3}) \cdot (X_{4} + X_{2} + X_{3}) \cdot (X_{4} + X_{2} + X_{3}) \cdot (X_{4} + X_{2} + X_{3}) \\ &= (X_{4} + X_{2} + X_{3}) \cdot (X_{4} + X_{2} + X_{3}) \cdot (X_{4} + X_{2} + X_{3}) \cdot (X_{4} + X_{2} + X_{3}) \\ &= (X_{4} + X_{2} + X_{3}) \cdot (X_{4} + X_{2} + X_{3}) \cdot (X_{4} + X_{2} + X_{3}) \cdot (X_{4} + X_{2} + X_{3}) \\ &= (X_{4} + X_{2} + X_{3}) \cdot (X_{4} + X_{2} + X_{3}) \cdot (X_{4} + X_{3} + X_{3}) \cdot (X_{4} + X_{3} + X_{3}) \cdot (X_{4} + X_{3} + X_{3}) \\ &= (X_{4} + X_{4} + X_{3} + X_{3} + X_{3} + X_{3} + X_{3} + X_{3}) \cdot (X_{4} + X_{3} + X_{$$

Какой из форм отдать предпочтение — определяется эффективностью минимизации Булевой функции. Обе формы абсолютно тождественны.

Числовой способ задания Булевых функций

Является наиболее компактным для задания Булевых функций, но крайне неудобен для их минимизации.

Также существует в двух вариантах (по единицам и по нулям).

### 1. По единицам:

в этом случае под знаком суммы в скобках через запятую перечисляются те номера наборов, где функция равна единице:

$$f_e = \Sigma (0,2,6)$$

$$f_g = \Sigma (0,4,5,6).$$

### 2. По нулям:

под знаком произведения в скобках через запятую перечисляются номера наборов, где функция равна нулю:

$$f_a = \Pi (1,4)$$

$$f_d = \Pi (1,4,7).$$

# § 1.4 Переход от алгебраической формы к структурной схеме, и наоборот. Функционально полные системы логических элементов

Для практической реализации Булевой функции надо от алгебраического способа ее представления перейти к структурной схеме.

Структурная схема — совокупность логических элементов с установленными между их входами и выходами связями. Структурная схема всегда представляется графически.

Основные элементы графики:

Элемент <u>И</u>:

$$\begin{array}{c|c} x_1 & \hline \vdots & & & F = x_1 \cdot x_2 \cdot \dots \cdot x_n \\ \hline x_n & & & & & \end{array}$$

Элемент ИЛИ:

$$\begin{array}{c|c} x_1 & \hline & 1 & F = x_1 + x_2 + \dots + x_n \\ \hline \vdots & \hline & \end{array}$$

Элемент НЕ:

### Исключающее ИЛИ (ХОК):

$$x_1$$

=1  $F = x_1 \oplus x_2 =$  (только две переменные)  $x_2$  =  $x_1 \cdot \overline{x}_2 + \overline{x}_1 \cdot x_2$

Сумма по модулю 2 – это исключающее ИЛИ над многими переменными (проверка на четность):

$$x_1 \oplus x_2 \oplus x_3 \oplus ... \oplus x_n$$

.

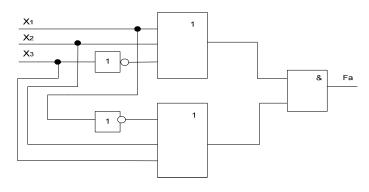

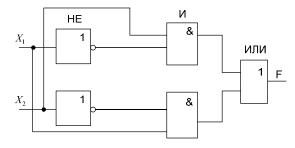

В качестве примера перейдем от алгебраических форм ранее рассмотренных функций к их структурным схемам:

$$f_a = (x_1 + x_2 + \overline{x}_3)(\overline{x}_1 + x_2 x_3)$$

$$f_e = \overline{\mathbf{x}}_1 \cdot \overline{\mathbf{x}}_2 \cdot \overline{\mathbf{x}}_3 + \overline{\mathbf{x}}_1 \cdot \mathbf{x}_2 \cdot \overline{\mathbf{x}}_3 + \mathbf{x}_1 \cdot \mathbf{x}_2 \cdot \overline{\mathbf{x}}_3$$

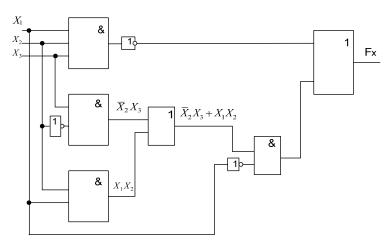

$$F_x = \overline{x_1 \cdot x_2 \cdot x_3} + \overline{x}_1 (\overline{x}_2 \cdot x_3 + x_1 \cdot x_2)$$

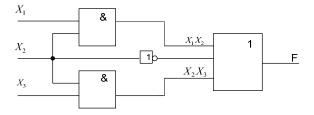

Обратный переход осуществляется от существующей структурной схемы к алгебраической форме.

### Пример:

$F = x_1 x_2 + x_2 x_3 + \overline{x}_2$  (т.е. идем наоборот, справа — налево).

При использовании интегральных технологий оказывается более технологичным, если в структурной схеме использовано меньшее количество функционально-разных логических элементов.

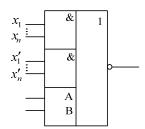

Оптимальным является вариант, когда задействован только какой-то один функциональный элемент, в связи с этим было разработано 5 функционально-полных систем логических элементов.

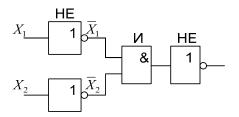

Под *функционально-полной системой* понимают такой набор логических элементов, с помощью которых можно реализовать любую Булеву функцию:

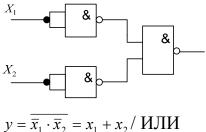

1. Набор: И, ИЛИ, НЕ.

Не достает только XOR:

$$F = x_1 \overline{x}_2 + \overline{x}_1 x_2 :$$

2. Набор: И, НЕ.

Не достает: ИЛИ, XOR.

Реализуем из имеющихся элементов операцию ИЛИ:

31

Используем теорему Де-Моргана:

$$\overline{x_1 x_2} = \overline{x}_1 + \overline{x}_2; \ \overline{x_1 + x_2} = \overline{x}_1 \cdot \overline{x}_2$$

ИЛИ:

$$F = x_1 + x_2 = \overline{\overline{x}_1 \cdot \overline{x}_2}$$

3. Набор: ИЛИ, НЕ.

Не достает: И, XOR.

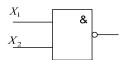

4. Набор: И – НЕ.

Не достает: И, НЕ, ИЛИ.

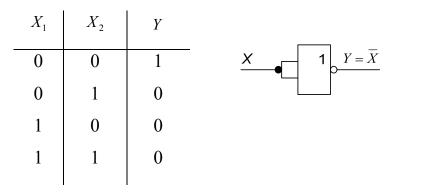

Составим таблицу истинности для элемента 2И – НЕ:

| $X_1$            | $X_2$ | Y |  |

|------------------|-------|---|--|

| 0                | 0     | 1 |  |

| 0                | 1     | 1 |  |

| 1                | 0     | 1 |  |

| 1                | 1     | 0 |  |

|                  |       |   |  |

| X <sub>1</sub> & |       |   |  |

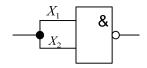

Если кружок на входе:

то это значит, что операция НЕ вы-

полняется над входной переменной.

### Создаем НЕ:

### Создаем И:

$$y' = \overline{x_1 \cdot x_2}$$

$y = \overline{y'} = \overline{x_1 \cdot x_2} = x_1 \cdot x_2$

### <u>ИЛИ</u>:

$$y = x_1 + x_2$$

Воспользуемся т. Де-Моргана:  $x_1 + x_2 = \overline{\overline{x}_1 \cdot \overline{x}_2}$  .

Нарисуем правую часть:

$$y - x_1 \cdot x_2 - x_1 + x_2 /$$

**FIJIP**

5. Набор: ИЛИ – НЕ.

HE:

§ 1.5 Минимизация Булевых функций. Карты Карно

Под *минимизацией Булевых функций* понимают упрощение исходного алгебраического выражения до вида, требующего для практической реализации минимального количества полупроводниковых структур.

Исходным для минимизации является алгебраическая форма представления Булевых функций. Процедура минимизации опирается на применение основных теорем Булевой алгебры. Критерием успешной минимизации является соотношение между исходным количеством полупроводниковых структур, и их количеством в окончательном варианте.

Количество полупроводниковых структур определяется по следующим правилам:

- Одни выход логического элемента И или ИЛИ эквивалентен одному полупроводниковому диоду.

- Операция НЕ эквивалентна одному полупроводниковому транзистору. Например:

Рассмотрим технологию минимизации на примерах (из предыдущего параграфа), исходная алгебраическая форма:

Пример 1:

$$F_e = \overline{x}_1 \cdot \overline{x}_2 \cdot \overline{x}_3 + \overline{x}_1 \cdot x_2 \cdot \overline{x}_3 + x_1 \cdot x_2 \cdot \overline{x}_3 =$$

$$3 \text{ тр.} \\ 12 \text{ диодов} \qquad \text{исходно}$$

$$= \overline{x}_1 \overline{x}_3 (\overline{x}_2 + x_2) + x_1 x_2 \overline{x}_3 + \overline{x}_1 x_2 \overline{x}_3 =$$

$$= \overline{x}_1 \overline{x}_3 + x_2 \overline{x}_3 (x_1 + \overline{x}_1) = \overline{x}_1 \overline{x}_3 + x_2 \overline{x}_3 =$$

$$= \overline{x}_3 (\overline{x}_1 + x_2)$$

$$\begin{vmatrix} 2 \text{ транзистора} \\ 4 \text{ диода} \end{vmatrix}$$

Всего 6 полупроводниковых структур

Минимизация завершена.

Пример 2:

$$F_a = (x_1 + x_2 + \overline{x}_3)(\overline{x}_1 + x_2 + x_3) \begin{vmatrix} = \\ 2 \text{ транзистора} \\ 8 \text{ диодов} \end{vmatrix}$$

$$= x_1\overline{x}_1 + x_1x_2 + x_1x_3 + x_2\overline{x}_1 + x_2x_2 + x_2x_3 + \overline{x}_3\overline{x}_1 + \overline{x}_3x_2 + \overline{x}_3x_3 =$$

$$= x_2(x_1 + \overline{x}_1 + 1 + \overline{x}_3 + x_3) + x_1x_3 + \overline{x}_1\overline{x}_3 =$$

$$= x_2 + x_1x_3 + \overline{x}_1\overline{x}_3 \begin{vmatrix} 2 \text{ транзистора} \\ 7 \text{ диодов} \end{vmatrix}$$

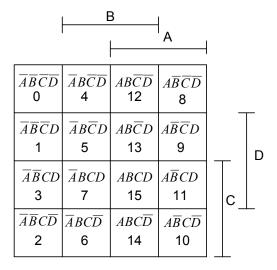

В тех случаях, когда количество переменных больше трех, удобнее пользоваться не последовательными алгебраическими вычислениями, а специальными картами, которые позволяют автоматизировать процесс минимизации. Это карты\_Карно.

Основополагающим для составления карт Карно является два термина.

*Ранг слагаемого* — это количество двоичных переменных, образующих элементарное произведение.

Соседние элементы — такие элементарные произведения, которые отличаются друг от друга только на одну инверсию. Например:  $x_1 \overline{x}_2 x_3$ .

Рассмотрим построение карт Карно на примере 4-х переменных. Вид шаблона карт Карно следующий:

А, В, С, D - двоичные переменные

Боковые и верхние ризки указывают на то, что переменные в этих полях при построении этих элементарных произведений берутся без инверсии, в противном случае – с инверсией. Каждая ячейка – элементарное произведение всех четырех переменных.

Запишем номер набора для этих четырех переменных.

Данный шаблон является основой для задания Булевой функции в виде карты Карно.

Исходным для заполнения является табличный или числовой способ задания Булевых функций. Там, где Булева функция принимает единичное значение, в номера тех наборов вписывается единица.

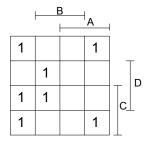

Например:

$$F_1 = \sum (0,8,5,13,10)$$

Соответствующая этой ф-ии карта Карно:

| 1 |   |   | 1 |

|---|---|---|---|

|   | 1 | 1 |   |

|   |   |   |   |

|   |   |   | 1 |

Например:  $F_2 = \sum (4,12,6,14)$

Соответствующая этой функции карта Карно:

| 1 | 1 |  |

|---|---|--|

|   |   |  |

|   |   |  |

| 1 | 1 |  |

Из шаблона видно, что расположенные в ячейках произведения являются соседними, включая крайние элементы карты. Т.е. при работе с ней всегда надо зрительно представлять ее в виде глобуса.

Автоматизм минимизации Булевой функции, записанной в виде карты Карно следующий:

- 1) Если единицами полностью заполнены две соседние строки или два соседних столбца, то в результате оставляется слагаемое первого ранга, состоящее из переменной, общей для этих областей.

- 2) Если на карте заполнены полностью строка или столбец, или четыре рядом стоящие ячейки, то в результирующем выражении оставляется слагаемое второго ранга, состоящее из элементов, общих для этих областей.

- 3) Если в карте Карно заполнены две соседние ячейки, то в конечном выражении оставляется слагаемое третьего ранга, состоящее из переменных, общих для этих обл.

- 4) Для отдельно заполненной единицей ячейки слагаемое четвертого ранга в результирующем выражении записывается полностью.

- 5) В процессе минимизации можно одну и ту же клетку задействовать несколько раз.

### Пример 1:

F = B

### Пример 2:

Результат минимизации  $F = \overline{B}\overline{D} + \overline{A}BD + CD\overline{A}$

В цифровой электронике все схемы делят на комбинационные и последовательные.

*Комбинационные* – схемы, которые математически полностью можно описать в рамках Булевой алгебры.

Последовательные — схемы, в которых используются элементы памяти, т.е. выходное состояние Булевой функции таких схем зависит от предыдущего состояния элемента памяти.

### Глава 2. Основы построения логических схем

## § 2.1 Импульсные сигналы: основные определения и терминология

В настоящее время в системах радио и проводной связи, в телевидении, радиолокации, в электронных вычислительных машинах и в других областях радиоэлектроники широко используются импульсные устройства. Напряжения и токи в таких устройствах имеют характер импульсов и перепадов.

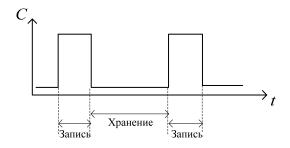

Электрическим импульсом называют напряжение (ток), отличающееся от постоянного уровня  $U_0$  в течение короткого промежутка времени (в частности, может быть  $U_0 = 0$ ). Понятие «короткий промежуток времени» является условным. Часто под этим понимают время, соизмеримое с длительностью переход-

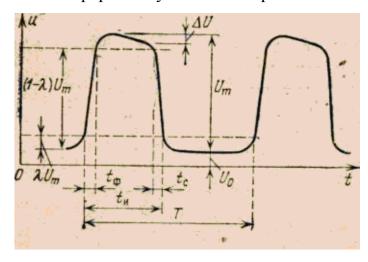

ных процессов в рассматриваемом устройстве. На рис. 2.1.1 показана одна из возможных форм импульсного напряжения:

Рис. 2.1.1

Наибольшее отклонение напряжения  $U_m$  от исходного уровня  $U_o$  называется aмплитудой (высотой) umnyльсa.

Участок импульса, на котором происходит отклонение напряжения от исходного уровня, называется фронтом, а участок импульса, где напряжение возвращается к исходному уровню — cnadom (срезом). В реальном импульсе, когда бывает трудно точно указать границы фронта и спада, их длительности  $t_{\phi}$  и  $t_{c}$  отсчитывают между определенными уровнями напряжения  $\lambda U_{m}$  и  $(1-\lambda)$   $U_{m}$ . Величина  $\lambda$  может быть различной. Обычно ее выбирают равной 0,05 или 0,1.

Длительность импульса  $t_u$  может измеряться на разных уровнях. Длительность импульса, отсчитываемая на уровне  $\lambda U_m$ , называется длительностью импульса по основанию, а на уровне  $(1-\lambda)U_m$  — длительностью импульса по вершине. Иногда длительность импульса определяется на уровне 0,5 от амплитудного значения. На рис. 2.1.1 указана длительность импульса по основанию.

Изменение напряжения  $\Delta U$  на вершине импульса называется неравномерностью (завалом) вершины.

Если импульсы следуют один за другим через равные промежутки времени, то в этом случае говорят о *периодической последовательности импульсов с периодом Т*.

Число импульсов, следующих в течение одной секунды, называется часто- moй noвторения umnyльсов F. Частота повторения, обратная периоду повторения импульсов, равна

$$F = 1/T. (1)$$

Периодическую последовательность импульсов обычно характеризуют коэффициентом заполнения или скважностью. *Коэффициент заполнения*  $\xi$  — это отношение длительности импульса к периоду его повторения:

$$\xi = t_u/T. \tag{2}$$

*Скважностью импульсов*  $\zeta$  называют отношение интервала между импульсами (скважины) к длительности самого импульса:

$$\zeta = (T - t_u)/t_u. \tag{3}$$

Если длительность импульса много меньше периода повторения, то скважность можно приближенно выразить через коэффициент заполнения:

$$\zeta \approx 1/\xi \tag{4}$$

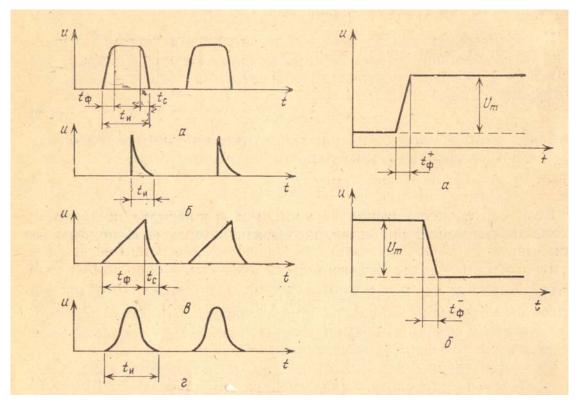

Импульсы могут иметь различную форму. Наибольшее распространение получили импульсы прямоугольной (трапецеидальной), треугольной и колоколообразной формы (рис. 2.1.2). Название форм является в значительной мере условным.

*Прямоугольными* (рис. 2.1.2, *а*) принято называть импульсы, у которых длительности фронта и спада меньше 1/10 длительности импульса. Если фронт или спад превышает эту величину, то импульсы называют *трапецеидальными*.

У *треугольных* импульсов длительность вершины равна нулю. Широкое распространение получили треугольные импульсы с коротким фронтом  $(t_{\phi} \approx 0)$  — *остроконечные* импульсы (рис. 2.1.2,  $\delta$ ), а также импульсы, у которых напряжение (ток) на фронте или спаде изменяется по линейному закону — *пилообразные* импульсы (рис. 2.1.2,  $\delta$ ).

*Колоколообразные* импульсы получили свое название благодаря специфической форме, напоминающей колокол (рис. 2.1.2,  $\varepsilon$ ).

Диапазон длительностей импульсов, с которыми приходится иметь дело в современной технике, достаточно велик и лежит в пределах от наносекунд (1 нс =  $10^{-9}$  c) до миллисекунд (1 мс =  $10^{-3}$  c) и более. Частота повторения может быть от единицы герц до сотен мегагерц.

Перепадами напряжения называют быстрые, практически скачкообразные изменения напряжения между двумя уровнями. Если в результате перепада напряжение изменяется от более низкого уровня к более высокому, то такой перепад называют положительным и, наоборот, если напряжение изменяется от более высокого уровня к более низкому, — отрицательным. Также определяются и перепады тока. На рис. 2.1.3, а, б показаны соответственно положительный и отрицательный перепады напряжения.

Разность уровней напряжения (тока) до и после перепада  $U_m$  называют величиной (амплитудой) перепада, а время изменения напряжения (тока) от одного уровня до другого — длительностью фронта перепада:  $\mathbf{t}_{\frac{1}{\phi}}$  — длительностью фронта положительного перепада,  $\mathbf{t}_{\frac{1}{\phi}}$  — длительностью фронта отрицательного перепада.

Рис. 2.1.2 Рис. 2.1.3

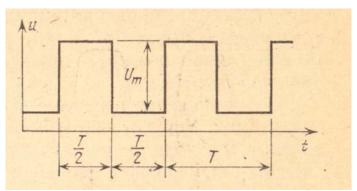

Периодически повторяющиеся положительные и отрицательные перепады напряжения образуют *напряжение прямоугольной формы*. В частном случае, когда перепады следуют через равные промежутки времени (рис. 2.1.4), напряжение прямоугольной формы называется *меандром*.

Рис. 2.1.4

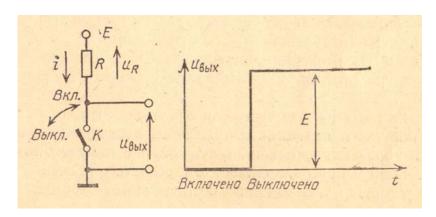

При формировании электрических импульсов и перепадов диоды, электронные лампы и транзисторы в схемах обычно работают в ключевом режиме. Ключевой режим характеризуется двумя состояниями этих приборов: «включено» — «выключено». Простейшие устройства, в которых осуществляется ключевой режим, называются ключевыми схемами (или коротко ключами). В общем виде идеализированная схема ключа и график ее выходного напряжения приведены на рис. 2.1.5:

Рис. 2.1.5

В положении «включено», когда контакты K замкнуты, можно, пренебрегая сопротивлением контактов, считать выходное напряжение равным нулю. В положении «выключено», когда контакты K разомкнуты, при отсутствии нагрузки ток i не протекает, падение напряжения  $u_R$  на резисторе R равно нулю и, следовательно, напряжение на выходе определяется напряжением источника питания E. Изменение напряжения на выходе при размыкании контактов происходит скачком. Рассмотренный режим работы ключа является идеальным. Мощность, рассеиваемая на коммутирующем приборе K этого ключа, равна нулю: при прохождении тока в положении «включено» равно нулю выходное напряжение, а в положении «выключено» при  $u_{\text{вых}} = E$  равен нулю ток.

В реальных ключах, когда в качестве коммутирующего устройства применяют полупроводниковый прибор или электронную лампу, уровни выходного напряжения, соответствующие состояниям «включено» и «выключено», зависят от типа коммутирующего прибора и переход из состояния «включено» в состояние «выключено» происходит не мгновенно, а в течение некоторого времени, обусловленного инерционными свойствами этого прибора и паразитными емкостями схемы. Это приводит к тому, что в реальных ключах мощность, рассеиваемая на коммутирующем приборе, отлична от нуля. Чем боль-

ше остаточное напряжение на нем в положении «включено» и чем больше время перехода ключа из положения «включено» в положение «выключено», тем больше рассеиваемая мощность. Уменьшение мощности рассеивания является первостепенной задачей для ключевой схемы, так как при этом уменьшается выделяемое ключом тепло, благодаря чему повышается надежность его работы и становится возможным увеличить плотность монтажа и уменьшить габариты аппаратуры, не прибегая к специальным мерам для отвода тепла.

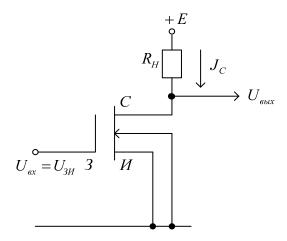

## § 2.2 Ключи на биполярных транзисторах

Простейшим цифровым устройством, имеющим самое широкое применение в цифровой электронике, являются *транзисторные ключи*.

Их назначение: усилитель мощности для импульсных сигналов. И дополнительно - согласователи сопротивлений или элемент, реализующий логическую операцию HE.

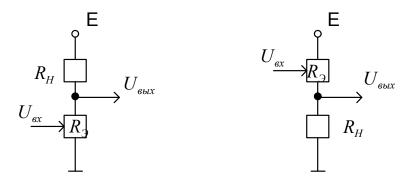

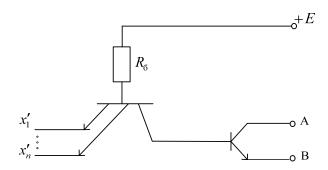

В общем виде ключ может быть представлен одной из следующих схем:

Где:  $R_H$  - элемент нагрузки ключа, в качестве которого обычно выступает либо активное сопротивление, либо полевой транзистор.

$R_{\rm 3}$  - регулирующий элемент, в качестве которого может выступать либо биполярный транзистор, либо полевой транзистор. Общим для них является то, что транзисторы обязаны работать в ключевом режиме.

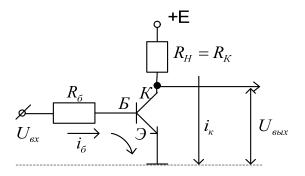

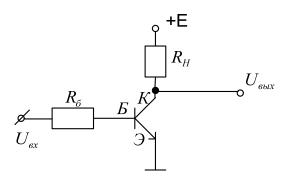

Рассмотрим основные схемы построения ключей на биполярных транзисторах:

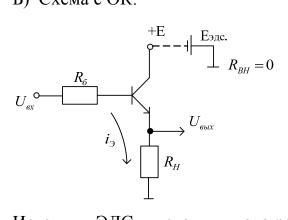

### А) Схема с ОЭ:

$U_{{\scriptscriptstyle E}\!{\scriptscriptstyle 9}} pprox 0,6 \div 0,7V$  - для германиевых структур.

$0.3 \div 0.4V$  - для кремниевых.

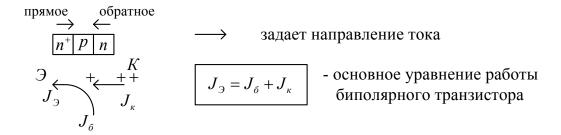

### Биполярный транзистор:

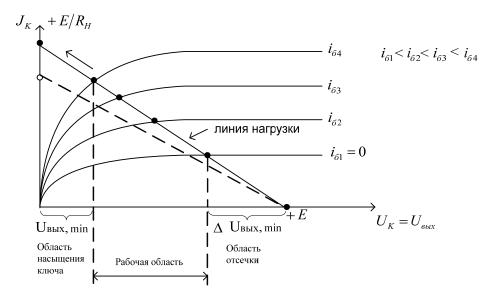

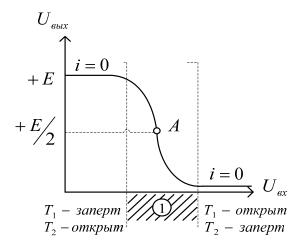

Если  $U_{ex} > 0$ , то благодаря возникновению  $J_{\delta} \neq 0$ , согласно основного уровня, обязаны возникнуть  $J_{\kappa}$  и  $J_{9}$ . При этом  $J_{\kappa} = \beta \cdot i_{\delta}$ ,  $\beta$ - статический коэффициент передачи тока для схемы с ОЭ. Тогда графическое соотношение между входным и выходным напряжениями следующее:

Для диодов Шотки:  $0,1 \div 0,15$  В.

Когда появится ток базы, обязаны появиться и  $i_{9}$ , и  $i_{K}$ .

Разность потенциалов, которая появится здесь - это падение напряжения на сопротивлении.

Или это величина (если ее провести через  $i_{\delta}$ ):

$$\Delta U = \beta i_{\delta} \cdot R_{H}$$

Эти режимы транзистора являются основой для построения ключей.

Как видно из диаграмм, если принять во внимание, что логической единице соответствует высокий уровень, а логическому минимуму — низкий, то данный ключ является инвертирующим, т.е дополнительно реализует логическую операцию НЕ (инвертор).

Ключи с ОЭ находят широкое применение для управления элементами индикации и коммутационными устройствами, а также в качестве преобразователей логических уровней.

Другое широкое применение ключа — получение входного устройства, со входным сопротивлением  $\approx R_{\delta}$ .

### Б) Схема с ОК:

Источник ЭДС и источник тока различаются внутренним сопротивлением.

У источника тока  $R_{\rm BH}

ightarrow \infty$  .

Рассмотрим работу такого ключа графически:

Обязан появиться  $J_{\Im}$ , но его появление приведет к появлению  $\mathbf{U}_{\text{\tiny GMX}} = \mathbf{i}_{\Im} \cdot \mathbf{R}_{\mathrm{H}} \,.$

Но если учесть, что  $i_3 \approx i_6 \cdot \beta$ , то данное устройство осуществляет усиление мощности сигнала при практически неизменной амплитуде выходного сигнала относительно входного. Поэтому такое устройство часто называют эммитерным повторителем.

Ключ является неинвертирующим (видно из диаграмм, т.е. логическая единица равна логической единице на выходе). Данный тип ключей используют в тех случаях, когда необходимо построить импульсное устройство с большим входным сопротивлением, поскольку:

$$R_{\rm gx} \approx R_{\rm 6} + \beta \cdot R_{\rm H}$$

$$U_{\rm none3} \pm R_{\rm 9K6} \cdot i_{\rm nomex}$$

$$i_{\rm 9} \approx i_{\rm 6} \cdot \beta$$

$$R_{\rm 9K6}$$

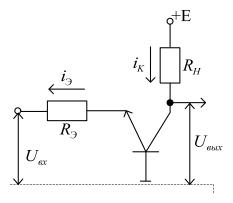

В) Схема с ОБ:

Рассмотрим работу такого ключа графически:

$$i_3 = i_6 + i_\kappa$$

Если пренебреч  $i_{\scriptscriptstyle \delta}$  , то  $i_{\scriptscriptstyle 9}=i_{\scriptscriptstyle K}$  , поэтому  $\Delta {\rm U} \approx i_{\scriptscriptstyle K}\cdot {\rm R}_{\rm H} \approx i_{\scriptscriptstyle 9}\cdot {\rm R}_{\rm H}$  .

Данное устройство часто используется в тех случаях, когда необходимо согласование с низкоомной линией со стороны приемника. Поскольку  $R_{\rm ex} \approx R_{_{9}}$ , а его можно сделать низкоомным или вообще убрать. С другой стороны устройство позволяет осуществить переход от одного уровня сигнала к другому. От  $-U_{\rm ex}$  к  $+U_{\rm essx}$  ( на входе отрицательный, на выходе - положительный сигнал). Как правило для этих целей ключ и используется.

Т.о. применение каждого из рассмотренных выше ключей определяется заданными значениями входного сопротивления, выходного сопротивления, полярностью входных и выходных сигналов, необходимостью реализации инверсии (т.е. операции НЕ).

Применительно к цифровым устройствам более часто применяются ключи с ОЭ.

## § 2.3 Переходные процессы в ключах с ОЭ

Исходными данными для анализа таких ключей является следующее:

1)

$$U_{ex}$$

, min

Заданные значения минимального входного напряжения, достигнув которое ключ полностью открывается (режим насыщения).

2)

$$U_{\text{\tiny BMX}}$$

, min

Минимальное значение выходного напряжения, в режиме когда ключ находится в насыщении.

3)

$$U_{ebix}^1 \leq +E$$

минимальные потери выходного напряжения, когда ключ в режиме отсечки.

4) Максимальное быстродействие ключа.

Первые три параметра удовлетворяются за счет расчета номиналов сопротивления базы и сопротивления нагрузки.

Алгоритм такого расчета:

Входная характеристика ключа с ОЭ следующая:

Для выполнения условия 2 рабочая точка – левая.

Как видно из графика, ключевой режим соответствует двум крайним областям работы транзистора. В идеальном случае в рабочей области он находиться не должен.

$U_{\it solx}$ , min достигается тогда, когда максимальный ток поступает в базу, или путем увеличения  $R_{\it H}$ , чтобы уменьшить наклон линии нагрузки. Но увеличение  $R_{\it H}$  приводит к росту  $\Delta U_{\it solx}$  min , которое равно  $\Delta U_{\it solx}$  min  $\approx R_{\it H} \cdot i_{\it ofp.kolnekmopa}$ . Поэтому при расчете транзисторного ключа выбирают такое значение  $R_{\it H}$ , чтобы по максимуму удовлетворить условие 2 и 3.

Выбор транзисторного элемента ключа завершен.

Для удовлетворения условия 1 надо выполнить расчет  $R_{\delta}$  из следующих соотношений:

Закон Ома:

$$i_{\sigma} = \frac{i_{\kappa}}{\beta} = \frac{+E/R_{H}}{\beta}$$

Этот ток будет обеспечен значением:

$$i_{\delta} = \frac{U_{\text{BX}}}{R_{\delta}} \implies U_{\text{min,ex}} = R_{\delta} \cdot i_{\delta} = \frac{R_{\delta}}{R_{\text{H}}} \cdot \frac{E}{\beta}$$

Откуда

$$R_{\delta} = \frac{U_{\text{min, BX}}}{F} \cdot \beta \cdot R_{H}$$

Таким образом,  $R_{\delta}$  должно быть не более этого значения.

Результат условия 4 достигается общим увеличением быстродействия ключа, который напрямую зависит от заряда, накапливаемого в базе.

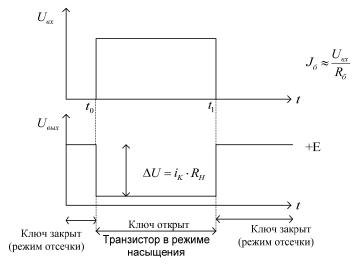

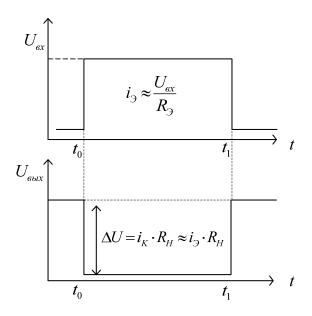

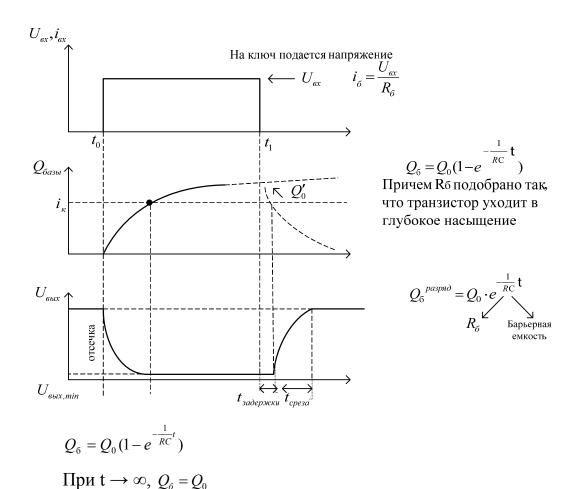

Рассмотрим причину снижения быстродействия с помощью следующих временных диаграмм:

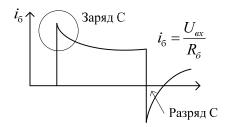

Достигнув некоторого значения 1, мы достигнем  $i_K = i_{K \max} = \frac{E}{R_K}$

Т.о. воздействие на ключ импульсного сигнала приводит к появлению трёх времён, которые ограничивают быстродействие ключа:

- 1)  $t_{\scriptscriptstyle \phi}$  длительность фронта, ограничивает  $f_{\scriptscriptstyle \mathrm{max}}$  .

- 2)  $t_{3adep>\!\!>\!\!<\!\!>>\!\!<}$  , которое удлиняет время нахождения ключа в насыщении.

- 3)  $t_{cpeзa}$ , которое так же ограничивает частоту воздействия импульсного сигнала.

Таким образом, чтобы увеличить быстродействие ключа и сделать его идеальным, необходимо свести к нулю эти три времени, ограничивающие быстродействие ключа.

Для сведения к минимуму трёх времён:  $t_{\phi}$ ,  $t_{3a\partial ep ж u}$ ,  $t_{cpesa}$ , в цифровой электронике используют три основных приёма:

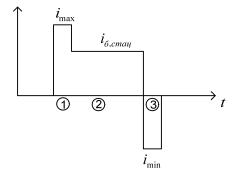

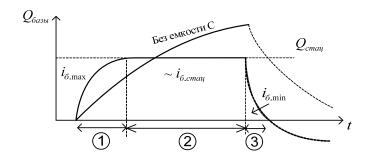

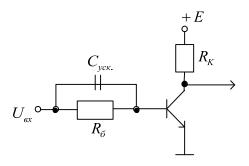

1) Использование в базе ускоряющих емкостей: Действительно, если подать в базу ток вида:

то ток  $i_{\text{max}}$  быстро зарядит базу, а ток  $i_{\text{min}}$  наоборот, приведёт к минимуму времени рассасывания заряда в базе.

При этом если подобрать значение  $i_{\delta.cmauцuoнарноe}$ , равное такому значению тока коллектора  $i_{\kappa o \pi}$ , при котором транзистор недонасыщен, то избыточный заряд в базе накапливаться не будет.

Данный достаточно простой приём сложно реализовать интегрально. Поэтому для увеличения быстродействия ключей, часто используют схемы с диодом в цепи обратной связи.

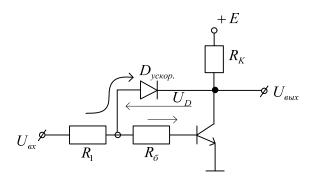

### 2) Ключ с ускоряющим диодом:

Основная идея заключается в следующем: при подаче импульса (т.е.  $i_{\delta_c} \neq 0$ ), диод закрыт и весь ток идёт в базу, что обеспечивает быстрое насыщение транзистора. По мере падения  $U_{\epsilon_{\delta d} x}$  наступает момент, когда диод открывается, и весь ток, создаваемый  $U_{\epsilon x}$ , течёт через него практически минуя базу.

Дальнейший принцип ускорения ключа аналогичен предыдущему.

$$i_{\delta} = \frac{U_{\text{ex}}}{R_{\text{l}} + R_{\delta}}$$

(до открывания D). Потом диод откроется, и:

$$i_{\delta} = \frac{U_D}{R_{\delta}} \cdot (U_D \approx 0.4(Si).$$

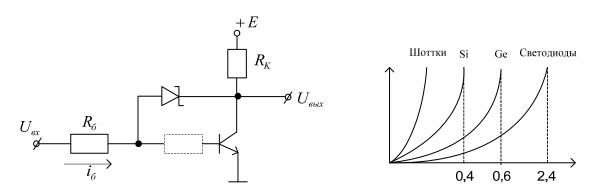

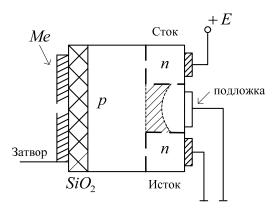

## 3) Ключ с диодами Шоттки:

Это полупроводник, где одним из граничных является метал (т.е. одна область – металл, а вторая – полупроводник n- или p- типа).

Отсутствие приграничного слоя => нет барьерной ёмкости.

Это очень быстродействующие диоды (BAX — как у обычного диода, но насыщение  $\sim 0.1$ В). Использование этих диодов в обратной связи транзисторного ключа автоматически исключает  $R_{\delta}$ . В результате получаем следующее:

При таком подходе так же автоматически исключается избыточное накопление зарядов в базе.

Логические элементы с диодами Шоттки являются самыми быстродействующими логическими элементами для схем с однополярным питанием.

## §2.4 Логические элементы на рыле и переключателях. Резисторнотранзисторная логика (РТЛ)